Notes of XI physics , Physics SEMICONDUCTORS.pdf - Study Material

Page 2 :

ELECTRONICS - SEMI CONDUCTOR, INTRODUCTION, The word "electronics' is derived from electron+dynamics which means the study of the behaviour of an electron, under different conditions of externally applied fields., That field of science which deals with electron devices and their utilization. an electronic device is "a device in, which conduction takes place by the movement of electron - through a vacuum, a gas or a semiconductor., Some familliar devices are :, (i) Rectifier, , (ii) Amplifier, , (iii) Oscillator etc., , Entertainment, , De fence, , Medical, , Telephone, , TV Broadcast, , Radar, , Telegraph, , Radio Broadcast, , Guided missiles, , Mobile phone, , VCR, VCD, , X-rays, , Ac, , E.E.G. (Electro Engio Graph), , FM mike, , ce, , Main application of electronics is computer which is used in every field., All electronics equipments required D.C. supply for operation (not A.C. supply), , en, , , , Electro cardio graph (ECG), CRO display, , FAX, , , , ad, em, , Communication, , y, , Application of Electronics, , ENERGY BANDS IN SOLIDS, , n=1, , 14 P, , CB, , n=3, n=2, n=1, , 1.1 eV, , band energy (eV), , JH, A', , n=3, n=2, , energy (eV), , S, , Sc, i, , Based on Pauli's exclusion principle, , VB, nd, , 2 band, st, , 1 band, , permissible energy, levels in isolated Si atom, , for singal silicon atom, , for Si material (Si crystal), , In an isolated atom electrons present in energy level but in solid, atoms are not isolated there is interaction, among each other due to this energy level splited into different energy levels., Quantity of these different energy levels depends on the quantity of interacting atoms., Splitting of sharp and closely compact energy levels result into energy band., This is decreate in nature., Order of energy levels in a band is 1023 and their energy difference = 10–23 eV., , , Energy Band, Range of energy possessed by electron in a solid is known as energy band., , JHA’S, Science Academy, , Page # 1

Page 3 :

, , , , , , Valence Band (VB), Range of energies possessed by valence electron is known as valence band., (a), Have bonded electron, (b), No flow of current due to such electron, (c), Always fulfill by electron, Conduction Band (CB), Range of energies possessed by free electron is known as conduction band., (a), Also called empty band of minimum energy., (b), In general Partially filled by electron., (c), If conduction Band is empty, then conduction is not possible., Forbidden Energy gap (FEG) (Eg), , , , Width of forbidden energy gap depends upon the nature of substance., , , , Width is more, then valence electrons are strongly attached with nucleus, , , , Width of forbidden energy gap is represented in eV., , band energy (eV), , ad, em, , y, , Eg = (C B)min – (V B)max, Energy gap between conduction band and valence band, where no free electron can exist., , forbidden, energy gap, valence band, , ce, , Ac, , , As temperature increases forbidden energy gap decreases (very slightly)., ACCORDING TO ENERGY BAND THEORY, Explanation of conductor, semiconductor and insulator :, , conduction band, , ~1eV, , Sc, i, , VB, , en, , overlaping, region, , VB, , semiconductor, (Si, Ge, GaAs etc), , VB, insulator, Diamond, wood etc., , Conductor, In some solids conduction band and valence band are overlapping so there is no band gap between them,, it means Eg = 0., Due to this a large number of electrons available for electrical conduction and therefore its resistivity is low, ( = 10–2 – 10–8 m) and conductivity is high [=102 – 108 (m)–1], Such materials are called conductors. For example gold, silver, copper etc., Insulator, In some solids energy gap is large (Eg > 3 eV)., So in conduction band there are no electrons and so no electrical conduction is possible. Here energy gap is so, large that electrons cannot be easily excited from the valence band to conduction band by any external energy, (electrical, thermal or optical)., Such materials are called as "insulator". Its = 108 m & = 10–8 m–1, Semiconductor, In some solids a finite but small band gap exists (Eg < 3eV)., Due to this small band gap some electrons can be thermally exicited to "conduction band"., These thermally excited electrons can move in conduction band and can conduct current their resistivity and, conductivity both are in medium range, =105 – 100 m and = 10–5 – 100 m–1, , JH, A', , , , >3eV, , S, , conductor, (Cu, Fe, Al, Na etc.), , CB, , CB, , CB, , , , , , JHA’S, Science Academy, , Page # 2

Page 4 :

, , CB, , band energy (eV), , 0.7 eV, VB, rd, , nd, , 2 band, , Si, , Si, , Si, , Si, , S, , Sc, i, , en, , EFFECT OF TEMPERATURE, At absolute zero kelvin temperature, At this temperautre covalent bonds are very, strong and there are no free electrons and, semiconductor behaves as perfect insulator., , JH, A', , Si, , VB, nd, , 2 band, , Ac, , 3 band, , 1.1 eV, , st, , 1 band, , ce, , band energy (eV), , CB, , Si, , ad, em, , y, , Example of semiconductor material, Elemental semiconductor, Compound semiconductor, Si, and G e, Inorganic, CdS, GaAs, CdSe, InP etc., Organic, anthracene, doped phalocyanines., Organic polymers, Poly pyrrole, Poly aniline, polythiophene, PROPERTIES OF SEMICONDUCTORS, , Negative temperature coefficient ( with increase in temperature resistance decreases, , Crystalline structure with covalent bonding [Face centred cubic (FCC)], , Conduction properties may change by adding small impurities, , Place in periodic table, , IV group (Generally), , Forbidden energy gap, (0.1 to 3 eV), , Charge carriers : electron and hole, , There are many semiconductors but few of them have practical application in electronics like, Ge32 : 2, 8, 18, 4, Si 14 : 2, 8, 4, , Above absolute temperature, With increase in temperature some covalent, bonds are broken and few valence electrons, jump to conduction band and hence it behave, as poor conductor., , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , hole, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , at 0 K, valence band conduction band, fully filled, fully empty, , at higher temperature, valence band conduction band, partially empty partially filled, , GOLDEN KEY POINTS, 3, , —, , Eg, , Number of electrons reaching from valence band to conduction band n = A T 2 e 2 kT, where k = Boltzmann constant = 1.38 10-23 J/K ,, T = absolute temperature,, A = constant, Eg = energy gap between conduction band and valence band, In silicon at room temperature out of 1012 Si atoms only one electron goes from valence band to conduction, band., In germanium at room temperature out of 10 9 Ge atoms only one electron goes from valence band to, conduction band., In semiconductors, Ohms law is aproximately obeyed only for low electric field (less than 106 Vm–1). Above this, field, the current becomes almost independent of applied field., , JHA’S, Science Academy, , Page # 3

Page 5 :

CONCEPT OF "HOLES" IN SEMICONDUCTORS, Due to external energy (temp. or radiation) when electron goes from valence band to conduction band (i.e., bonded electrons becomes free), vacancy of free e– create in valence band. This electron vacancy called as"hole", Which have same charge as electron but positive, this positively, charged vacancy moved randomly in semiconductor solid., Properties of holes :, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , It is missing electron in valence band., , hole, , It acts as positive charge., It is effective mass is more than electron., , Si, , Si, , Si, , Si, , Si, , Si, , Si, , Si, , ad, em, , Hole acts as virtual charge, although there is no physical charge on it., , y, , It is mobility of hole is less than electron., , Hole Current, , At room temperature, due to breaking of some Covalant bonds some free electrons are produced. By applying, electric field current flow due to free electrons. This current called hole current., , Ac, , EFFECT OF IMPURITY IN SEMICONDUCTOR, , Doping is a method of addition of "desirable" impurity atoms to pure semiconductor to increase conductivity of, semiconductor., , ce, , GOLDEN KEY POINTS, The concentration of dopant atoms be very low, doping ratio is vary from, to, , 1 : 10 10, , In general it is 1 : 108, , en, , impure : pure :: 1 : 106, , There are two main method of doping., Alloy method, , (ii), , Diffusion method (The best), , Sc, i, , (i), , S, , The size of dopant atom (impurity) should be almost the same as that of crystal atom. So that crystalline, structure of solid remain unchanged., , JH, A', , CLASSIFICATION OF SEMICONDUCTOR, , Intrinsic semiconductor, , (pure form of Ge, Si), ne = nh = ni, , Extrinsic semiconductor (doped semicondutor), N-type, pentavalent impurity, (P. As, Sb), donor impurity (ND), ne >> nh, , P-type, trivalent impurity, (Ga, B, In, Al), acceptor impurity (NA), nh >> ne, , N-type semiconductor, When a pure semiconductor (Si or Ge) is doped by pentavalent impurity (P, As, Sb, Bi) then four electrons out, of the five valence electrons of impurity take part, in covalent bonding, with four silicon atoms surrounding it and, the fifth electron is set free. These impurity atoms which donate free e – for conduction are called as Donor, impurity (ND). Here free e– increases very much so it is called as "N" type semiconductor. Here impurity ions, known as "Immobile Donor positive Ion". "Free e–"called as "majority" charge carriers and "holes" called as, "minority" charge carriers., , JHA’S, Science Academy, , Page # 4

Page 6 :

extra, e–, Si, , Sb, , Si, , Si, , Si, , Si, , Si, , Sb, , Si, , Sb, , Si, , Si, , Si, , Si, , Si, , Si, , hole, , electron, , ND = immobile donor, positive ion, , P-type semiconductor, When a pure semiconductor (Si or Ge) is doped by trivalent impurity (B, Al, In, Ga) then outer most three, , ad, em, , y, , electrons of the valence band of impurity take part, in covalent bonding with four silicon atoms surrounding it, and except one electron from semiconductor and make hole in semiconductor. These impurity atoms which, accept bonded e– from valance band are called as Acceptor impurity (NA). Here holes increases very much so it, is called as "P" type semiconductor here impurity ions known as "Immobile Acceptor negative Ion". Free e– are, called as minority charge carries and holes are called as majority charge carriers., , Si, , Al, , Si, , Si, , Si, , Si, , Si, , Al, , Si, , Al, , Si, , Si, , Si, , Si, , Si, , Si, , Ac, , hole, , 1., , en, , N-type (Pentavalent impurity), , CB, , 2., , 3., , JH, A', , VB, , P-type(Trivalent impurity), , CB, donor, impurity, level, , S, , CB, , NA = immobile acceptor, negative ion, , Sc, i, , Intrinsic Semiconductor, , electron, , ce, , hole, , VB, , VB, , acceptor, impurity, level, , free, electron, positive, donor ion, , hole, negative, acceptor, ion, , Mainly due to electrons, , Mainly due to holes, , 4., , Current due to, electron and hole, ne = nh = ni, , nh << ne (ND ~ ne), , nh >> ne (NA ~ nh), , 5., , I = Ie + Ih, , I ~ Ie, , I ~ Ih, , 6., , Entirely neutral, , Entirely neutral, , Entirely neutral, , 7., , Quantity of electrons, , Majority - Electrons, , Majority - Holes, , and holes are equal, , Minority - Holes, , Minority - Electrons, , JHA’S, Science Academy, , Page # 5

Page 7 :

MASS ACTION LAW, In semiconductors due to thermal effect, generation of free e– and hole takes place., A part from the process of generation, a process of recombination also occurs simultaneously, in which free, e– further recombine with hole., At equilibrium rate of generation of charge carries is equal to rate of recombination of charge carrier., The recombination occurs due to e– colliding with a hole, larger value of n e or nh, higher is the probability of their, recombination., Hence for a given semiconductor rate of recombination ne × nh, so, , rate of recombination = R ne × nh, , where, , R = recombination coefficient,, , The value of R remains constant for a solid, according to the law of thermodynamics until crystalline lattice, structure remains same., , y, , For intrinsic semiconductor ne = nh = ni, R ne × nh = R ni2, , r, , ad, em, , rate of recombination = R n i2, , so, , ni2 = ne × nh, , Under thermal equilibrium, the product of the concentration 'n e' of free electrons and the concentration n h of, holes is a constant., , mass action law, , E , , Sol . (a), , hc, (in eV), e, E, , so E , , 1 2 40 0, , , (E is in eV and is in Å), , = 5890 Å, , 1 24 0 0, 2.1eV, 5890, , JH, A', , S, , so, , (b), , E, at a temperature of 300 K., kT, , en, , (b) the value of, , ce, , The energy of a photon of sodium light ( = 589 nm) equals the band gap of a semiconducting material., Find : (a) the minimum energy E required to create a hole-electron pair., , Sc, i, , Ex., , ne × nh = ni2, , Ac, , Independent of the amount of doping by acceptor and donor impurities., , E, 2.1 1.6 10 19 J, , 81, kT 1.38 10 23 300, , Ex., , A P type semiconductor has acceptor level 57 meV above the valence band. What is maximum wavelength of, light required to create a hole ?, , Sol ., , E, , hc, , , r, , , , 6.62 10 3 4 3 10 8, hc, =, = 217100 Å, E, 57 10 3 1.6 10 19, , A silicon specimen is made into a p-type semiconductor by doping on an average one indium atom per 5 × 107, silicon, atoms., If the number, density of atoms in, the silicon, specimen is, 28, 3, 5 × 10 atoms/m ; find the number of acceptor atoms in silicon per cubic centimeter., Sol . The doping of one indium atom in silicon semiconductor will produce one acceptor atom in p-type semiconductor., Since one indium atom has been dopped per 5 × 10 7 silicon atoms, so number density of acceptor atoms in, Ex., , silicon, , , , 5 10 28, 10 2 1 atom/m 3 = = 1015 atoms/cm 3, 5 10 7, , JHA’S, Science Academy, , Page # 6

Page 8 :

The concentration of hole - electron pairs in pure silicon at T = 300 K is 7 x 1015 per cubic meter. Antimony is, doped into silicon in a proportion of 1 atom in 107 Si atoms. Assuming that half of the impurity atoms contribute, electron in the conduction band, calculate the factor by which the number of charge carriers increases due to, doping the number of silicon atoms per cubic meter is 5 x 1028., , Sol . In pure semiconductor electron-hole pair = 7 × 1015 /m 3, after doping donor impurity ND =, So, , nfinal = nh + ne, , Ex., , 5 10 2 8, N, 5 10 21 and n e D 2.5 10 21, 7, 10, 2, , nfinal, , ne 2.5 × 1021 ( ne >> nh), , n final n initial 2.5 1 0 21 1 4 1 0 1 5 2 .5 1 0 2 1, , , = 1.8 × 105, n initial, 1 4 10 15, 14 1 0 15, , ad, em, , Factor =, , r, , total charge carrier ntotal initial = nh + ne = 14 × 1015, , y, , Ex., , Pure Si at 300 K has equal electron (n e) and hole (nh) concentrations of 1.5 × 1016 m –3. Dopping by indium, increases nh to 3 × 1022 m–3. Calculate ne in the doped Si., , n 2i, (1 .5 1 0 16 )2, , = 7.5 × 109 m–3, hh, 3 1 0 22, , ce, , ne , , Ac, , Sol . For a doped semi-conductor in thermal equilebrium n enh = n 2i (Law of mass action), , , , en, , RESISTIVITY AND CONDUCTIVITY OF SEMICONDUCTOR, Conduction in conductor, , , , A, , Sc, i, , Relation between current (I) and drift velocity (vd ), , E= V, , , I = ne A vd n = number of electron in unit volume, , , , drift velocity of electron vd = E, , , , Conductivityne, , Mobility, , , , V, , I, amp/m 2 = ne vd, A, , S, , J =, , JH, A', , current density, , , , J = ne E = E, Resistivity, , Vd, E, , Conduction in Semiconductor, Intrinsic semiconductor, , P - type, , N - type, , ne = nh, , nh >> ne, , ne >> nh, , J = ne [ ve + vh], , J e nh vh, , J e ne ve, , , , 1, = en [ e + h ], , , JHA’S, Science Academy, , , , 1, e nh h, , , , , 1, e ne e, , , Page # 7

Page 9 :

GOLDEN KEY POINTS, Due to impurity the conductivity increases approximately 105 times, sc = e + h = neee + nh eh, Ex., , What will be conductance of pure silicon crystal at 300K Temp.. If electron hole pairs per cm3 is 1.072 x 1010, at this Temp, n = 1350 cm2 / volt sec & P = 480 cm2 / volt sec, , Sol . = niee + nieh = nie ( e + h) = 3.14×10–6 mho/cm, Pure Si at 300 K has equal electron ne and hole nh concentration of 1.5 × 1016/m3. Doping by indium increases, nh to 4.5 × 1022/m3. Calculate n e in doped silicon., , Sol . ne =, , A semiconductor has equal electron and hole concentration of 6 × 108/m 3. On doping with certain impurity, electron concentration increases to 9 × 10 12/m 3., , y, , Ex., , n 2i, (1.5 10 16 )2, , 5 10 9 m 3, nh, (4.5 10 22 ), , (i), , Identify the new semiconductor obtained after doping., , (ii), , Calculate the new hole concentration., , (ii), , , , n 2i, , n enh, , , , nh =, , Ac, , Sol . ni = 6 × 108/m 3 and ne = 9 × 1012 /m 3, (i), ne > ni so it is N-type semiconductor, , ad, em, , Ex., , n 2i, 36 10 16, , = 4 × 104 /m3, ne, 9 10 12, , P-type, , , , indium buttom, , liquid, , N-type, , JH, A', , arsenic, , Sc, i, , N-type, , indium, , S, , indium, , en, , ce, , P - N JUNCTION, Techniques for making P-N junction, Alloy Method, Here a small piece of III group impurity like indium is placed over n–Ge or n–Si and melted as shown in figure, ultimetely P – N junction form., , arsenic, , n, , PN J, , N-type, , arsenic buttom, , liquid, , P-type, , n, , PN J, , P-type, , Diffusion Junction, , A heated P–type semiconductor is kept in pentavalent, impurity vapours which diffuse into P–type, semiconductor as shown and make P–N junction., Vapour deposited junction or epitaxial junction, , heat, , vacuum, N-type Ge/Si, , Al, vapours, , n, , P-N J, , diffused, P-type layer, , If we want to grow a layer of n–Si or p–Si then p–Si, wafer is kept in an atmosphere of Silane (a silicon, compound which dissociates into Si at high, , to vacuum, pump, , temperatures) plus phosphorous vapours., On craking of silane at high temperature a fresh layer on n–Si grows on p–Si giving the "P–N junction"., Since this junction growth is layer by so it is also referred as layer growth or epitaxial junction formation of P–N junction., , JHA’S, Science Academy, , Page # 8

Page 10 :

DESCRIPTION OF P-N JUNCTION WITHOUT APPLIED VOLTAGE OR BIAS, Given diagram shows a P–N junction immediately after it is formed., p, , P region has mobile majority holes and immobile negatively, , n, , charged impurity ions., N region has mobile majority free electrons and immobile, positively charged impurity ions., Due to concentration difference diffusion of holes starts from, P to N side and diffusion of e– s starts N to P side., , p, , n, , Due to this a layer of only positive (in N side) and negative, (in P–side) started to form which generate an electric field (N, to P side) which oppose diffusion process, during diffusion, magnitude of electric field increases due to this diffusion it, gradually decreased and ultimately stopes., , ad, em, , y, , d, , The layer of immobile positive and negative ions, which have no free electrons and holes called as depletion, layer as shown in diagram., GOLDEN KEY POINTS, , Width of depletion layer 10 -6 m, (a), As doping increases depletion layer decreases, (b), As temperature is increased depletion layer also increases., (c), P-N junction unohmic, due to nonlinear relation between I and V., , , , Potential Barrier or contact potential, for, Ge 0.3 V,, for, Si 0.7 V, , , , Electric field, produce due to potential barrier E V 0.56, r E 105 V/m, d 10, This field prevents the respective majority carrier from crossing barrier region, , Sc, i, , en, , ce, , Ac, , , , p, , n, , hole, , free electron, charge, density, , JH, A', , S, , DIFFUSION AND DRIFT CURRENT, (1), Diffusion current : P to N side, (2), Drift current : N to P side, If there is no biasing then diffusion current = drift current, So total current is zero, – +, , deplition layer, (10–6), , +, distance, , distance, , electric, potential, , electric, field, intensity, , –, , V0 = 0.2V, distance, , JHA’S, Science Academy, , Page # 9

Page 11 :

BEHAVIOUR OF P–N JUNCTION WITH AN EXTERNAL VOLTAGE APPLIED OR BIAS, Forward Bias, If we apply a voltage "V" such that P–side is positive and N–side is negative as, shown in diagram., P, , The applied voltage is opposite to the junction barrier potential., , , , V, VB, , Due to this effective potential barrier decreases, junction width also decreases, so more, majority carriers will be allowed to flow across junction. It means the current flow in, principally due to majority charge carries and is large (mA) called as forward Bias., Reverse Bias, , N, , V, VB, , If we apply a voltage "V" such that P–side is negative and N–side is positive as, P, , N, , GOLDEN KEY POINTS, , ad, em, , y, , shown in diagram., The applied voltage is same side of to the junction barrier potential. Due to this, effective potential barrier increased junction width also increased, so no majority, carriers will be allowed to flow across junction., Only minority carriers will drifted. It means the current flow in principally due to minority charge carries and is, very small (mA) called as reversed Bias., , In reverse bias, the current is very small and nearly constant with bias (termed as reverse saturation current)., However interesting behaviour results in some special cases if the reverse bias is increased further beyond a, certain limit, above particular high voltage breakdown of depletion layer started., , , , Breakdown due to covalent breaking of depletion layer termed as Zener breakdown (After the discovery, C., Zener) and such a diode is Zener diode., , ce, , Ac, , , , There is another variant of Zener like breakdown if the doping concentrations of p–and n–sides are not as high, as for the case of zener diode. Such diodes will have relatively wider junction widths. At very high reverse bias,, already existing electrons and holes are accelerated in the junction field and may undergo many collisions (like, nuclear chain reaction) with the atoms in the crystal., , Sc, i, , , , en, , Zener diodes with different breakdown voltages (for regulations of different voltages) can obtained by changing, the doping concentration of its p–and n–sides., , JH, A', , S, , These new electron-hole pairs created by impact ionisation also get accelerated in the junction field and collide, further with the crystal atoms giving an increasing number of new electrons and holes. These bias beyond a, certain critical value. This phenomenon is known as Avalanche breakdown and the device is referred to as, Avalanche diode., Zener Break down, , Avalanche Break down, , Where covalent bonds of depletion layer, its, , Here covalent bonds of depletion layers are bro, , self break, due to high electric field of very, , ken by collision of "Minorities" which aquire, , high Reverse bias voltage., , high kinetic energy from high electric field of, very-very high reverse bias voltage., , This phenomena predominant, , This phenomena predominant, , (i) At lower voltage after "break down", , (i) At high voltage after breakdown, , (ii) In P – N having "High doping", , (ii) In P – N having "Low doping", , (iii) P – N Jn. having thin depletion layer, , (iii) P – N Jn. having thick depletion layer, , Here P – N not demage paramanently, "In D.C voltage stablizer zener phenomena, is used"., , JHA’S, Science Academy, , Here P – N damage peramanentaly due ot ', "Heating effect" due to abruptly increament of, minorities during repeatative collisoins., , Page # 10

Page 12 :

Forward Bias, , Reverse Bias, , positive, negative, , P, N, , P, , negative, positive, , P, N, , N, , P, , N, , V, +, , V, –, , –, , 1., , +, , 1., , Potential Barrier reduces, , 2., , Width of depletion layer decrease, , 3., , P-N Junction Provide very small resistance, , 3., , P-N Junction Provide high resistance, , 4, , Forward current flow in circuit, , 4., , Very small current flow., , 5., , Order of forward current in milli amp., , 5., , Order of current in micro amp. (Ge), , y, , Width of depletion layer increases., , ad, em, , 2., , Potential Barrier increases., , or Neno amp. (Si)., Mainly flow majority current flows., , 7., , Forward characteristic curves., , 6., , Mainly minority current flows, 7., , Ac, , 6., , Reverse characteristic curve, , ce, , VR (volt), , Rf , , 9., , Vf, 100 , If, , S, , Forward resistance, , 2.1, , JH, A', , 8., , 0.7, 1.4, Vp (volt), , Knee or cut in voltage, Ge 0.3 V ,, , JHA’S, Science Academy, , IR, break down (A), voltage, , Sc, i, , knee, voltage, 0, , I0, , en, , ip, (mA), , Si 0.7 V, , 8., , Reverse resistance, RB , , 9., , VB, 10 6 , IB, , Breakdown voltage, Ge 25 V,, , Si 35 V, , Page # 11

Page 13 :

CHARACTERISTIC CURVE OF P-N JUNCTION DIODE, A, , P, , K, , N, , A, , K, symbol, , (0-10)V, , , , +, , , , D, , –, , R, , Rh, , If mA, , + mA, –, , A, , , D, , , , , C, R, , Rh, , O, Reverse, saturation, current, , Forward, bias, A, V, Volt, Knee, voltage, , D, , Reverse bias, , y, , Forverd bias, , B, , Breakdown, voltage, VB, , Ir A, , (0-1)V, +, –, , Ac, , ad, em, , In forward bias when voltage is increased from 0V in steps and corresponding value of current is measured, the, curve comes as OB of figure. We may note that current increase very sharply after a certain voltage knee, voltage. At this voltage, barrier potential is completely eliminated and diode offers a low resistance., In reverse bias a microammeter has been used as current is very very small. When reverse voltage is increased, from 0V and corresponding values of current measured the plot comes as OCD. We may note that reverse, current is almost constant hence called reverse saturation current. It implies that diode resistance is very high. As, reverse voltage reaches value VB, called breakdown voltage, current increases very sharply., For Ideal Diode, , in reverse bias, , ce, , in forward bias, on switch, , Rr = , off switch, , Sc, i, , RECTIFIER, , en, , Rf = 0 , , It is device which is used for converting alternating current into direct current., Half wave rectifier, , JH, A', , S, , , , For positive half cycle, , For negative half cycle, , During the first half (positive) of the input signal. Let S1 is at positive and S2 is at negative potential. So, the PN, junction diode D is forward biased. The current flows through the load resistance R L and output voltage is, obtained., During the second half (negative) of the input signal, S1 and S2 would be negative and positive respectively. The, PN junction diode will be reversed biased. In this case, practically no current would flow through the load, resistance. So, there will be no output voltage., Thus, corresponding to an alternating input signal, we get a unidirectional pulsating output., Peak inverse voltage (PIV) Vs = Vin, In half wave rectifier PIV = maximum voltage across secondary coil of transformer, , JHA’S, Science Academy, , Page # 12

Page 14 :

, , Full wave rectifier, When the diode rectifies the whole of the AC wave, it is called full wave rectifier. Figure shows the experiemental, arrangement for using diode as full wave rectifier. The alternating signal is fed to the primary a transformer. The, output signal appears across the load resistance RL ., , D1 D2 D1 D2 D1 D2 D1, , For positive half cycle, , For negative half cycle, , During the positive half of the input signal :, , y, , Let S1 positive and S2 negative., , ad, em, , In this case diode D1 is forward biased and D2 is reverse biased. So only D1 conducts and hence the flow of, current in the load resistance RL is from A to B., During the negative half of the input signal :, , Now S1 is negative and S2 is positive. So D1 is reverse-biased and D2 is forward biased. So only D2 conducts and, hence the current flows through the load resistance RL from A to B., , Ac, , It is clear that whether the input signal is positive or negative, the current always flows through the load resistance, in the same direction and full wave rectification is obtained., , ce, , Bridge Rectifier, , S, , Sc, i, , en, , , , JH, A', , During positive half cycle, , (i), , input frequency = 50Hz, , JHA’S, , D1,D4, , D2,D3, , D1,D4, , D2 and D3 are foward biased on switch, D1 and D4 are reverse biased off switch, , For half wave rectifier, , input, , Science Academy, , D2,D3, , During negative half cycle, , D1 and D4 are foward biased on switch, D2 and D3 are reverse biased off switch, , D1,D4, , output, , ripple frequency = 50Hz, , Page # 13

Page 15 :

(ii), , for full wave rectifier, , input, , output, , input frequency = 50Hz, Pulse, (i), For half wave rectifier, , ripple frequency = 100Hz, , input, , output, , number of pulse = 100, , y, , For full wave rectifier, , ad, em, , (ii), , number of pulse = 50, , input, , output, , number of pulse = 100, , Ac, , number of pulse = 100, FILTER CIRCUIT, , Capacitor Filter, , Sc, i, , AC + DC, , en, , , , ce, , To reduce A.C. Components, , AC, , DC, , C, output, , , , JH, A', , S, , output of rectifier, , L - C Filter, , DC + low AC, , DC, , AC + DC, AC, output of rectifier, , JHA’S, Science Academy, , C, output, , Page # 14

Page 16 :

, , - Filter (Best Filter), DC + low AC, DC, AC + DC, AC, , C1, , AC, , C2, , output, approx pure D.C, , output of rectifier, , ZENER DIODE, , It is always connected in reverse biased condition manner., , , , en, , SOME SPECIAL DIODES, , ce, , Ac, , + Fluctuating, input, , In forward biased it works as a simple diode., , Photodiode, , +, , RS, , RL, , regulated, output, , , Zener, voltage V Reverse bias, Z, , Reverse current, , Used as a voltage regulation, , Symbol of, Zener diode, , ad, em, , as Zener diode., , y, , A properly doped crystal diode which has sharp break down voltage is known, , Sc, i, , A junction diode made from “light or photo sensitive semiconductor” is called a “photo diode” its symbol, , S, , When light of energy "h'' falls on the photodiode (Here h > energy gap) more electrons move from valence, band, to conduction band, due to this current in circuit of photodiode in "Reverse bias", increases. As light, intensity is increased, the current goes on increases so photo diode is used, "to detect light intensity" for example, it is used in "Vedio camera"., Light emitting diode (L.E.D), When a junction diode is “forward biased” energy is released at junction in the form of light due to recombination, of electrons and holes. In case of Si or Ge diodes, the energy released is in infra-red region., In the junction diode made of GaAs, InP etc energy is released in visible region such a junction diode is called, , JH, A', , , , ., , "light emitting diode" (LED) Its symbol, , , Solar cell, Solar cell is a device for converting solar energy into electrical. A junction diode in which one of the P or N, sections is made very thin (So that the light energy falling on diode is not greatly asorbed before reaching the, junction) can be used to convert light energy into electric energy such diode called as solar cell. Its symbol, (i), (ii), , It is operated into photo voltaic mode i.e., generation of voltage due to the bombardment of optical, photon., No external bias is applied., , JHA’S, Science Academy, , Page # 15

Page 17 :

(iii), , , Active junction area is kept large, because we are intrested in more power. Materials most commonly used for, solar cell is Si, As, Cds, CdTe, CdSe, etc., Variable capacitor (Varactor), P – N junction diode can be used as a "Capacitor" here depletion layer acts as "dielectric material" and remaining, "P" and "N" part acts as metallic plates., , ], , , , its symbol, , , , (ii), , V, 0 .5 V, , = 10 6 volt/m, L 5 1 0 7, , Work energy theorm, , P, , ad, em, , E, , y, , Diode laser, It is intersting form of LED in which special construction helps to produce stimulated radiation as in laser., Ex. A potential barrier of 0.5 V exists across a p-n junction (i) If the depletion region is 5 × 10–7 m wide. What is the, intensity of the electric field in this region ? (ii) An electron with speed 5×105 m/s approaches the p-n junction, from the n-side with what speed will it enter the p-side., V, E=, Sol .: (i), Width of depletion layer L = 5 × 10–7 m, L, , 1, 1, Mv2i eV Mv2f, 2, 2, , N, , Mv2i 2 eV, = 2.7 × 10 5 m/s, M, Ex. Figure shows a diode connected to an external resistance and an e.m.f. Assuming that the barrier potential, developed in diode is 0.5 V1 obtain the value of current in the circuit in milliampere., Sol . E = 4.5 V, R = 100 , 100, voltage drop across p-n junction = 0.5 V, , ce, , Ac, , vf , , effective voltage in the circuit V = 4.5 – 0.5 = 4.0 V, , en, , V 4.0, , 0 .04 A = 0.04 × 1000 mA = 40mA, R 1 00, , 4.5V, , JH, A', , S, , Sc, i, , current in the circuit I , , JHA’S, Science Academy, , Page # 16

Page 18 :

TRANSISTOR, , E, , N, , P, , N, , NPN, C, E, , Sc, i, , l, , en, , ce, , Ac, , ad, em, , y, , Inventor William Bradford Shockley, John Bardeen and Walter Houser Brattain., Transistor is a three terminal device which transfers a singal from low resistance circuit to high resistance circuit., It is formed when a thin layer of one type of extrinsic semiconductor (P or N type is sandwitched between two, thick layers of other two type extrinsic semiconductor., Each transistor have three terminals which are :(i), Emitter, (ii), Base, (iii), Collector, Emitter, It is the left most part of the transistor. It emit the majority carrier towards base. It is highly doped and medium, in size., Base, It is the middle part of transistor which is sandwitched by emitter (E) and collector (C). It is lightly doped and very, thin in size., Collector, It is right part of the transistor which collect the majority carrier which is emitted by emitter. It have large size and, moderately doped., There are two semiconductor junction in transister, (i), The junction between emitter and base is known as emitter-base junction (JEB)., (ii), The junction between base and collecter is known as base-collector junction (JCB)., TRANSISTOR ARE OF TWO TYPES, l, N-P-N Transistor, If a thin layer of P-type semiconductor is sandwitched between two thick layers of N-type semiconductor is, known as NPN transistor., , B, , B, , P-N-P Transistor, , C, , JH, A', , S, , If a thin layer of N-type of semiconductor is sandwitched between two thick layer of P-type semiconductor is, known as PNP transistor., E, , PNP, P, , N, , C, , P, , E, , C, B, , B, , WORKING OF NPN TRANSISTOR, The emitter Base junction is forward bias and collector base junction is reversed biased of N-P-N transistor in, circuit (A) and symbolic representation is shown in Figure., emitter-base, junction, , collector-base, junction, , h, mA, , JHA’S, Science Academy, , mA, , Page # 17

Page 19 :

collector-base, junction, , ce, , Ac, , emitter-base, junction, , ad, em, , y, , When emitter base junction is forward bias, electrons (majority carriers) in emitter are repelled toward base., The barrier of emitter base junction is reduced and the electron enter the base, about 5% of these electron, recombine with hole in base region result in small current (IB)., The remaining electron ( 95%) enter the collector region because they are attracted towards the positive, terminal of battery results collecter current (IC), For each electron entering the positive terminal of the battery is connected with collector base junction an, electron from negative terminal of the battery connected with emitter base junction enters the region., The emitter current (IE) is more than the collector (IC)., The base current is the difference between IE and IC and proportional to the number of electron hole recombination, in the base., IE = IB +IC, WORKING OF PNP TRANSISTOR, When emitter-base junction is forward biased holes (majority carriers) in the emitter are repelled towards the, base and diffuse through the emitter base junction. The barrier potential of emitter-base junction decreases and, hole enter the n-region (i.e. base). A small number of holes ( 5%) combine with electron of base-region resulting, small current (IB). The remaining hole ( 95%) enter into the collector region because they are attracted towards, negative terminal of the battery connected with the collector-base junction. These hole constitute the collector, current (IC)., , mA, , en, , mA, , Sc, i, , As one hole reaches the collector, it is neutralized by the battery. As soon as one electron and a hole is, neutralized in collector a covalent bond is broken in emitter region. The electron hole pair is produced. The, released electron enter the positive terminal of bettary and hole more towards the collector. So IE = IB + IC, CHARACTERISTIC OF TRANSISTOR, , l, , JH, A', , S, , To study about the characterstics of transistor we have to make a circuit [i.e. JEB Forward bias and JCB , Reverse bias] we need four terminals. But the transistor have three terminals. By keeping one of the terminal of, transistor is common in input and output both. So the transistor is connected in three ways in circuit., (i), Common base connector (ii), Common emitter (iii), Common collector, In these three common emitter is widely used and common collector is rarely used., Common emitter characterstics of a transistor, Input characterstics, The variation of base current (IB) (input) with base emitter voltage (VEB) at constant-emitter voltage (VCE) is called, input characterstic., , IB(A), , 75, 50, , VC =, E 5, V, , 100, , VC =, E 0, V, , input characteristic curves, , 25, 0, 0.2 0.4 0.6 0.8 0.8, VBE (volt), , JHA’S, Science Academy, , Page # 18

Page 20 :

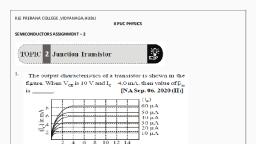

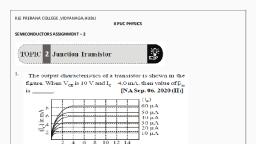

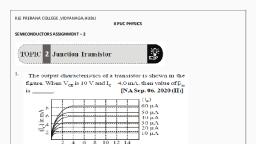

l, , (i), Keep the collector-emitter voltage (VCE) constant (say VCE = 1V), (ii), Now change emitter base voltage by R1 and note the corresponding value of base current (IB)., (iii), Plot the graph between VEB and IB., (iv), A set of such curves can be plotted at different VCE (say VCE = 2V), Output characterstics, , 0 A, IB= 10, , 10, , The variation of collector current IC (output) with collector-emitter, , IB = 75A, , 8, , IC(mA), , voltage (VCE) at constant base current (IB) is called output characterstic., I = 50A, 6, (i), Keep the base current (IB) constant (say IB = 10A), 4, I = 25A, (ii), Now change the collector-emitter voltage (V CE ) using variable, 2, I =0, resistance R2 and note the corresponding values of collector, 1 2 3 4, 5, current (IC)., VCE(volt), (iii), Plot the graph between (VCE versus IC), (iv), A set of such curves can be plotted at different fixed values of base current (say 0, 20 A, 30 A etc.), B, , B, , GOLDEN KEY POINTS, , Transistor have two P-N Junction JEB and JCB. On the bases of junction condition transistor work in four regions., E, , n, , p, , ce, , B, , C, , Collector-Base, , Region of working, , Forward biased, , Reverse biased, , Active, , Forward biased, , Inverse Active, , Reverse biased, , Cut off, , Forward biased, , Saturation, , en, , Emitter-Base, , Reverse biased, , Emitter, , High dopping, , Smallest size, , Low dopping, , Largest size, , Medium dopping, , JH, A', , Base, , Medium size, , S, , Forward biased, , Sc, i, , Reverse biased, , , , n, , Ac, , , , ad, em, , y, , B, , Collector, , , , The collector region is made physically larger than the emitter. Because collector has to dissipiate much, greater power., , , , Transistor all mostly work in active region in electronic devices & transistor work as amplifier in Active region, only., , , , Transistor i.e. It is a short form of two words "Transfer resistors". Signal is introduced at low resistance circuit, and out put is taken at high resistance circuit., , , , Base is lightly doped. Otherwise the most of the charge carrier from the emitter recombine in base region and, not reaches at collector., , , , Transistor is a current operated device i.e. the action of transistor is controlled by the motion of charge carriers., i.e. current, , JHA’S, Science Academy, , Page # 19

Page 21 :

TRANSISTOR AS AN AMPLIFIER, The process of increasing the amplitude of input signal without distorting its wave shape and without changing, its frequency is known as amplification., A device which increases the amplitude of the input signal is called amplifier., IC, C, , –, , B, , RL, , IB, , Vo, , E V, CE, Vi, , IE, , common emitter amplifier, NPN transistor, , –, VBB, , y, , +, , –, , IC, , IB, , +, VCC, , amplifier, , + amplified, output signal, , Comparative study of transistor configuration, 1. Common Base (CB), 2. Common Emitter (CE), , 3. Common Collector (CC), , C B, , CE, , E, , C, , B, , C, , CE, , B, , B, IE, , E, , IC, , E, , B, , Low (100 ), , Output resistance, , Very High, , Current Gain, , (AI or ), , Sc, i, , JH, A', , S, , IC, = I , E, , Voltage Gain, , AV , , Vo, IC R L, =, Vi, IE R i, , Av = , , RL, Ri, , , Power Gain, , Ap , , E, , Po, Pi, , same phase, , C, , C, , B, , IE, , E, , IB, IC, , C, , C, , Very High 750 k, , High, , Low, , (AI or ), , (AI or ), , IC, = I , B, , IE, = I , B, , AV , , Vo, IC R L, =, Vi, IB R i, , Av= , , Ap , RL, Ri, , E, CC, , High (750 ), , RL, Ri, , AV , , Vo, IE R L, =, Vi, IB R i, , Av = , , , , A p 2, , Phase difference, , IE, , E, , en, , Input Resistance, , IB, , ce, , B, , B, , C, , IC, , B, IB, , CC, , Ac, , CB, , ad, em, , intput, signal, , RL, Ri, , less than 1, Po, Pi, , A p 2, , Ap , RL, Ri, , opposite phase, , Po, Pi, , Ap 2, , RL, Ri, , same phase, , (between output, and input), Application, , JHA’S, Science Academy, , For High Fequency, , For Audioable fequency, , For Impedance Matching, , Page # 20

Page 22 :

Relation Between and , , , , , , , IE = I B + I C, , IE = I B + I C, , IE = I B + I C, , divide by IC, , divide by IB, , 1+, , IE IB, , 1, IC IC, , IE, I, 1+ C, IB, IB, , , , 1 1, +1, , , , , 1, 1 –, , , 1–, , , , , , Ac, , , , GOLDEN KEY POINTS, In transistor charge carriers move from emitter to collector. Emitter send the charge carriers and collector, collect them this happen only when emitter-base junction is forward bias and collector-base junction is reverse, bias (base of amplifier), In transistor reverse bias is high as compared to forward bias so that the charge carriers move from emitter to, base exert a large attractive force to enter in collector region so base current is very less., CE configuration is widely used becasue it have large voltage and power gain as compared to other amplifiers., In amplifier negative feed back is used to stabilized the gain., CC is used for impdence matching for connecting two transistors in cascade., , ce, , , , ad, em, , y, , , , , 1 –, , en, , Q . 1 A transistor is a current operated device. Explain why ?, Ans. The action of a transistor is controlled by the charge carriers (electrons or holes). That is why a transistor is a, current operated device., , Sc, i, , Q . 2 In a transistor, reverse bias is quite high as compared to the forward bias. Why ?, Ans. In a transistor, charge carriers (electrons or holes) move from emitter to collector through the base. The reverse, bias on collector is made quite high so that it may exert a large attractive force on the charge carriers to enter, the collector region. These moving carriers in the collector constitute a collector current., , Q.4, , JH, A', , S, , Q 3 A transistor is a temperature sensitive device. Explain., Ans. In a transistor, conduction is due to the movement of current carriers electrons and holes. When temperature of, the transistor increases, many covalent bonds may break up, resulting in the formation of more electrons and, holes. Thus, the current will increase in the transistor. This current gives rise to the production of more heat, energy. the excess heat causes complete breakdown of the transistor., The use of a transistor in common-emitter configuration is preferred over the common-base configuration., Explain why ?, Ans. The current gain and hence voltage gain in the common-emitter configuration is much more than i of commonbase configuration. Hence the former is preferred over the later., Q . 5 Why to we prefer transistor over the vacuum tubes in the portable radio receivers ?, Ans. This is because of two reasons :, (i), Transistor is compact and small in size than the vacuum tube., (ii), Transistor can operate even at low voltage which can be supplied with two or three dry cells., Q . 6 Why a transistor cannot be used as a rectifier ?, Ans. If transistor is to be used as a rectifier the either emitter-base or base-collector has to used as diode. For equated, working of the said set of diodes, the number density of charge carriers in emitter and base or base and collector, must be approximately same. As base is lightly doped and comparatively thin, so emitter cannot work as a, rectifier., , JHA’S, Science Academy, , Page # 21

Page 23 :

Ex., , In a transistor, the value of is 50. Calculate the value of ., , Sol ., , , , , 1 , , , 1 , , r 50 =, , r 50 – 50 = , , r , , 50, = 0.98, 51, , Ex. Calculate the emitter current for which IB = 20 A, = 100, Sol . IC = IB = 100 × 20 × 10–6 = 2000 A, IE = IB + IC = 20 + 2000 = 2020 A = 2.02 × 10–3 A = 2.02 mA, For a common emitter amplifier, current gain = 50. If the emitter current is 6.6 mA, calculate the collector and, base current. Also calculate current gain, When emitter is working as common base amplifier., , , IC, IB, , IE = I C + I B, , , , IC = IB = 50IB, , using equation (i) we get, , Hence IC = 50 ×, , 6 .6, = 6.47 mA, 51, , ...(i), 6.6 = 50 IB + IB = 51 IB, , , , and, , IB , , r, , 50, , 0.98, =, 51, 1 , , 6 .6, = 0.129 mA, 51, , y, , Sol . , , ad, em, , Ex., , Transistor with = 75 is connected to common-base configuration. What will be the maximu collector current, for an emitter current of 5 mA ?, Sol . = 75, Ie = 5 mA, IC, IE, , , , en, , , , IC, 3, , 30, 30, =, = 30, , = 0.97, , , IB, 0 .1 0 0, 1 1 30 31, , IB = 20 A = 0.02 mA , IC = 0.5 mA, , S, , (b), , IC = IE =, , 75, × 5 = 4.93 mA, 76, , and, , IE =, , IC 3 3 1, , = 3.1 mA, , 30, , IC, 0.5, ac I 0.02 25, B, , JH, A', , In npn transistor circuit, the collector current is 10 mA. If 95% of the electrons emitted reach the collector, what, is the base current ?, , Sol . IC = 95% IE = 0.95 IE IE =, Now IE = IC + IB, Ex., , , , The base current is 100 A and collector current is 3 mA., (a) Calculate the values of , IE and , (b) A change of 20 A in the base current produces a change of 0.5 mA in the collector current. Calculate a.c.., , Sol . (a), , Ex., , , , Sc, i, , Ex., , , 75, 75, , =, 1 , 1 75 7 6, , ce, , , , Ac, , Ex., , , , IC, 0.95, , , , 1 00, 10 mA = 10.53 mA, 95, , IB = IE – IC = 10.53 – 10 = 0.53 mA, , In an NPN transistor 1010 electrons enter the emitter in 10–6 s and 2% electrons recombine with holes in base,, then current gain and are :, , 10 10 1.6 10 19, Ne, =, = 1.6 mA, t, 10 6, 2, 1.6 = 0.032 mA, Base current IB =, 1 00, but IE = IC + IB, , IC = IE – IB = 1.6 – 0.032 = 1.568 mA, , Sol . Emitter current IE =, , , , , , IC 1.568, , 0.98, IE, 1.6, , JHA’S, Science Academy, , and, , , , IC 1.568, , 49, IB 0.032, , Page # 22

Page 24 :

FEEDBACK, Feedback are two types :, l, , Positive feedback, When input and output are in the same phase then positive feedback is there. It is used in oscillators., , l, , Negative feedback, If input and output are out of phase and some part of that is feedback to input is known as negative feedback., It is used to get constant gain amplifier., , TRANSISTOR IN AN OSCILLATOR, Oscillator is device which delivers a.c. output wave form of desired frequency from d.c. power even without, input singal excitation., The electric oscillations are produced by L– C circuit, , y, , ad, em, 3, , T2, L, 4, , C, , mutual inductance, (coupling through, magnetic field), , T'2 output, , , , , , n-p-n, , Ac, , (i.e. tank circuit containing inductor and capacitor)., These oscillations are damped one i.e. their amplitude, decrease with the passage of time due to the small, resistance of the inductor. In other words, the energy, of the L – C oscillations decreases. If this loss of energy, is compensated from outside, then undamped, oscillations (of constant amplitude) can be obtained., , T1, , 1, 2, , S1 (switch), , This can be done by using feed back arrangement and a transistor in the circuit., , ce, , L – C circuit producing L – C oscillations consists of an inductor of inductance L and capacitor of, , en, , variable capacitance C inductor of inductance L' is connected in the collector-emitter circuit through a battery, and a tapping key (K). Inductors L and L' are inductively coupled (Figure), , Sc, i, , Working, , When key K is closed, collector current begins to flow through the coil L. As this current grows, magnetic flux, linked with coil L increase (i.e. changes)., , S, , Since coil L is inductively coupled with L, so magnetic flux linked with coil L' also changes. Due to change in, , JH, A', , magnetic flux, induced e.m.f. is set up across the coil L'., The direction of induced e.m.f. is such that the emitter-base junction is forward biased. As a result of this biasing,, emitter current IE increases which in turn increases the collector current IC [IE = IB + IC]., With the increase in collector current, magnetic flux linked with coil L also increases. This increases the e.m.f., induced in the coil L'., , The increased induced e.m.f. increases the forward bias of emitter-base junction. Hence emitter current is, further increased which in turn increases the collector current. The process of increasing the collector current, continues till the magnetic flux linked with coil L' becomess maximum (i.e. constant). At this stage, the induced, e.m.f. in coil L' becomes zero., The upper plate of the capacitor C gets positively charged during this process., When induced e.m.f. becomes zero, the capacitor C starts discharging through the inductor L., The emitter current starts decreasing resulting in the collector current. With decreasing collector current which, flows through L', e.m.f. is again induced in the coil L' but in the opposite direction. It opposes the emitter current, and hence collector current ultimately decreases to zero., , JHA’S, Science Academy, , Page # 23

Page 25 :

The change in magnetic flux linked with coil L' stops and hence induced e.m.f. in the coil L becomes zero. At this, stage, the capacitor gets discharged through coil L but now in the opposite direction. Now the emitter current, and hence collector current increase but now in the opposite direction ., This process repeats and the collector current oscillates between maximum and minimum values., Oscillating frequency f , , 1, 2 LC, , ADVANTAGES OF SEMICONDUCTOR DEVICES OVER VACUUM TUBES, Advantages, Semiconductor devices are very small in size as compared to the vacuum tubes. Hence the circuits using, semiconductor devices are more compact., , , , In vacuum tubes, current flows when the filament is heated and starts emitting electrons. So, we have to, wait for some time for the operation of the circuit. On the other hand, in semiconductor devices no, heating is required and the circuit begins to operate as soon as it switched on., , , , Semiconductor devices require low voltage for their operation as compared to the vacuum tube. So a lot, of electrical power is saved., , , , Semiconductor devices do not produce any humming noise which is large in case of vacuum tube., , , , Semiconductor devices have longer life than the vacuum tube. Vacuum tube gets damaged when its, filament is burnt., , , , Semiconductor devices are shock proof., , , , The cost of production of semiconductor-devices is very small as compared to the vacuum tubes., , , , Semiconductor devices can be easily transported as compared to vacuum tube., , ce, , en, , Disadvantage s, , Semiconductor devices are heat sensitive. They get damaged due to overheating and high voltages. So, they have to be housed in a controlled temperature room., , , , The noise level in semiconductor devices is very high., , , , Semiconductor devices have poor response in high frequency range., , Sc, i, , , , Why is a transistor so called ?, , S, , Q.1, , Ac, , ad, em, , y, , , , Q.2, , JH, A', , Ans. The word Transistor can be treated as short form of two words 'transfer resistor'. In a transistor, a signal is, introduced in the low resistance circuit and output is taken across the high resistance circuit. Thus, a transistor, helps to transfer the current from low resistance part to the high resistance part., The base region of a transistor is lightly doped. Explain why ?, or, , In a transistor, the base is lightly doped. Explain why ?, Ans. In a transistor, the majority carriers (holes or electrons) from emtter region move towards the collector region, through base. If base is made thick and highly doped, then majority of carriers from emitter will combine with, the carriers in the base and only small number of carriers will reach the collector. Thus the output or collector, current will be considerably small. To get large output or collector current, base is made thin and lightly doped, so that only few electron-hole combination may take place in the base region., Q.3, , Explain why the emitter is forward biased and the collector is reverse biased in a transistor ?, , Ans. In a transistor, the charge carriers move from emitter to collector. The emitter sends the charge carriers and, collector collects them. This can happen only if emitter is forward biased and the collector is reverse biased so, that it may attract the carriers., , JHA’S, Science Academy, , Page # 24

Page 26 :

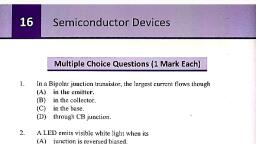

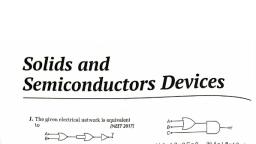

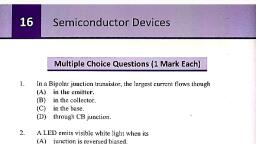

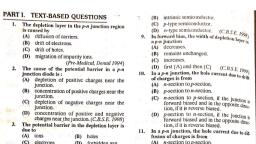

PREVIOUS, 1., , EXAMS, , QUESTIONS, , In a full wave rectifier if input frequency is 50 Hz, then output ripple frequency will be :–, (1) 50 Hz, , 8., , EXERCISE–I, Current in the circuit will be :–, , [RPET 2000, AIPM T 03], , 20, , (2) 100 Hz, , 30, , (3) 200 Hz, 2., , [AIPM T 2001], , (4) 25 Hz, , GaAs :–, , I, 20, , [RPM T 2000], , 5V, , (1) elemental semiconductor, 5, 40, , (3), , 5, 10, , (4) metallic semiconductor, 3., , Best representation of PN juntion –, (1), , [RPM T 2000], , 9., , (2), , (2), , 5, 50, 5, 20, , y, , (3) insulator, , (1), , (4), , ad, em, , (2) compound semiconducor, , Two wires P and Q made up of different materials, have same resistance at room temperature. When, heated, resistance of P increases and that of Q, decreases. We conclude that:–, [MP PET 2001], , Ac, , (1) P and Q both are conductors but because of, being made of dif f erent materials it, happens so, , (3), , ce, , (2) P is n-type semiconductor and Q is p-type, semiconductor, , Sc, i, , (1), , (2), , (3), , (4), , Find VAB :–, , (3) P is semiconductor and Q is conductor, (4) P is conductor and Q is semicondcutor, , [RPM T 2000], , S, , 5., , Symbol of zener diode :–, , JH, A', , 4., , en, , (4), , 10., , A full wave rectifier circuit along with the input and, output voltage is shown in the figure then output, due to diode(2) is :–, [MP PET 2001], +, , 1, RL, , [RPM T 2000], , 2, , (1) 10V, , (2) 20V, , 30V, , A, , (3) 30V, , (4) none, 6., , 7., , 10, , 10, , +, , 10, , B, , If ne and nh are the number of electrons and holes, in a semiconductor heavily doped with phosphorus,, then :–, [KCET 2001], , (1) A, C, , (2) B, D, , (1) ne > > nh, , (2) ne < < nh, , (3) B, C, , (4) A, D, , (3) ne < nh, , (4) ne = nh, , The resistance of a reverse biased pn junction diode, is about :–, [KCET 2001], (1) 1 ohm, , (2) 102 ohm, , (3) 103 ohm, , (4) 106 ohm, , JHA’S, Science Academy, , A B C DE F G, , 11., , The ratio of resistance for forward to reverse bias, of P–N junction diode is :, [M P PET 2000, 2001], (1) 102 : 1, , (2) 1 : 104, , (3) 1 : 10–4, , (4) 10–2 : 1, Page # 25

Page 27 :

12., , In a n-p-n transistor circuit, the collector current is, 10 mA. If 90% of the electrons emitted reach the, collector, the emitter current (IE) and base current, (IB) are given by :–, [KCET 2001], , 19., , (1) IE = 1mA; IB = 11 mA, , 20., , (1) 25 Hz, , (2) IE = 11 mA ; IB = 1 mA, (4) IE = 9 mA ; IB = –1 mA, In a p-n junction :-, , [AIPMT 2002], , 21., , The electrical circuit used to get smooth DC output, from a rectifier circuit is called :–, [KCET 2003], , 22., , In the case of constants and of a transistor :–, (1) , , (2) , , (3) = 1, , (4) , , In the following common emitter configuration an, 'npn' transistor with current gain = 100 is used, the output voltage of amplifier will be :–, , ad, em, , (3) p and n both are at same potential, (4) undetermined, For the given circuit of p-n, , diode, , R, , junction diode which is, correct :–, , Ac, 1mV, , V, , (3) in F.B. the voltage across R is 2 V, (4) in R.B. the voltage across R is 2 V, (2) 0.48, , (3) 0.61, , (4) 2.14, , 23., , [RPM T 2002], , Sc, i, , (1) 1.21, , en, , Ripple coefficient of a half wave rectifier is :–, , Reverse bias applied to a junction diode :–, (1) lowers the potential barrier, , [AIPM T 2003], , 24., , S, , (2) raises the potential barrier, , JH, A', , (2) collector is positive and emitter is negative with, respect to the base, , 25., , A semiconductor wire is connected in an electric, circuit in series and temperature of system increased, then the current in the system :–, [RPM T 2003], (1) decreases, , (2) constant, , (3) increases, , (4) will not flow, , Correct statement for diode is :–, , [RPM T 2003], , Barrier potential of a p-n junction diode does not, depend on :–, [AIPMT 2003], (1) diode design, , (2) temperature, , (3) forward bias, , (4) doping density, , A semiconductor is damaged by a strong current,, because :–, [BHU 1997], (1) lack of free electrons, (2) decrease in electrons, (3) excess of electrons, , (4) both collector and emitter are negative with, respect to the base, , JHA’S, , (4) 10 V, , (4) full wave rectifier in bidirecational, , (3) collector is positive and emitter is at same, potential as the base, , Science Academy, , (3) 1.0 V, , (3) efficiency of full wave rectifier and half wave, rectifier is same, , [AIPM T 2003], , (1) both collector and emitter are positive with, respect to the base, , 18., , (2) 0.1 V, , (2) in full wav e rectifier both diodes work, simultaneously, , (4) increases the minority carrier current, A n-p-n transistor conducts when :–, , (1) 10 mV, , (1) in full wave rectifier both diodes work alternatively, , (3) increases the majority carrier current, , 17., , Vout, , 1k, , ce, , (2) in R.B. the voltage across R is V, , 16., , [AIIM S 2003], , 10k, , (1) in F.B. the voltage across, R is V, , 15., , (2) oscillator, (4) amplifier, , y, , (2) high potential is at p side and low potential is at, n side, , (3) 70.7 Hz (4) 100 Hz, , [KCET 2003], , (1) high potential is at n side and low potential is at, p side, , 14., , (2) 50 Hz, , (1) filter, (3) logic gate, , (3) IE = –1 mA; IB = 9 mA, 13., , If a full wave rectifier circuit is operating from 50, Hz mains, the fundamental frequency in the ripple, will be :–, [AIPM T 2003], , (4) none of these, 26., , On increasing the reverse bias to a large value in, p-n junction diode then value of current [BHU 2002], (1) remains fixed, , (2) increases slowly, , (3) decrease slowly, , (4) suddenly increase, , Page # 26

Page 28 :

27., , In semiconductor, at room temperature :–, , 35., , (1) valence band are partially empty and conduction, band are partially filled, [AIPM T 2004], (2) valence band are fully filled and conduction band, are partially empty, (3) valence band are fully filled, , 36., , When two semiconductor of p and n type are, brought in to contact, they form a p-n junction which, acts like a :–, [Haryana PM T 2003], (1) rectifier, , (2) amplifier, , (3) oscillator, , (4) conductor, , Efficiency of a HW rectifier is nearly :–, [Haryana PM T 2004], , (4) conduction band are fully empty, In half wave rectifier peak value of sinusodial signal, is 10V. Determine D.C. component at output :–, , (1) 80%, 37., , [AIPM T 2004], , (1), , (2), , 10, V, , , (4), , 20, V, , , 2, In p-n junction photocell electromotive force due to, monochrometic light is proportional to [AIPMT 2004], (2) intensity of light, , (3) frequency of light, , (4) p-n applied voltage, , In a p-n junction the depletion layer of thickness, 10–6 m has potential across it is 0.1 V. The electric, field is (V/m) :–, [UP CPM T 2001], –6, , (1) 10, , (2) 10, , 5, , y, , (1) diffusion of charges, (2) depends upon the nature of material, , (4) both drift and diffusion of charges, 38., , (4) 10, , [RPM T 2004], , (2) holes, , ce, , (4) none of these, , In an intrinsic semiconductor, number of electrons, and holes at room temperature are :–, (2) zero, , (3) unequal, , (4) infinity, , Sc, i, , (1) equal, , In germanium crystal, the forbidden energy gap in, joule is :–, [Delhi PM T 2003], , 39., , (1) intrinsic, , (2) extrinsic, , (3) p-type, , (4) n-types, , In a forward biased p-n junction diode, the potential, barrier in the depletion region is of the form :–, [KCET 2004], , (2) zero, (4) 1.76 × 10–19, , V, , JH, A', , (3) 1.12 × 10–19, , 40., , When the conductivity of a semiconductor is only, due to breaking of cov alent bonds, the, semiconductor is called :–, [KCET 2001], , S, , (1) 1.6 × 10–19, 33., , In a p-type semicondutor, there are mainly :–, (1) free electrons, , [UP CPMT 2001, Jipmer 2001], , 32., , When a junction diode is reverse biased, the flow of, current across the junction is mainly, due to :–, [VM M C 2003], , (3) both (1) and (2), , –5, , (3) 10, , (4) 20%, , (3) drift of charges, , (1) p-n potential barrier, , 7, , 31., , (3) 10V, , (3) 40%, , Ac, , 30., , V, , en, , 29., , 10, , (2) 60%, , ad, em, , 28., , The probability of electrons to be found in the, conduction band of an intrinsic semiconductor at a, finite temperature :–, [Delhi PM T 2004], , V, , (1), , (2), p, , (1) decreases exponentially with increasing band gap, , n, , p, , V, , n, V, , (2) increases exponentially with increasing band gap, (3), , (3) decrease with increasing temperature, , p, , (4) is independent of the temperature and the band gap, 34, , Assuming that the junction diode is ideal the current, through the diode is :–, [Haryana PM T 2000], 3V, , 100, , 1V, , (1) 200 mA, , (2) 20 mA, , (3) 2 mA, , (4) zero, , (4), , 41., , n, , p, , When a transistor is used in a circuit :, , n, [BHU 1995], , (1) both junctions are forward biased, (2) emitter base junction is forward biased and the, base collector junction is reverse biased, (3) emitter base junction is reverse biased and the, base collector junction is forward biased, (4) both junctions are reverse biased, , JHA’S, Science Academy, , Page # 27

Page 29 :

42., , In a transistor, the base is made very thin and lightly, doped with an impurity :–, [BHU 2001], , 48., , For a transistor in a common emitter arrangement, the alternating current gain is given by :–, , (1) to save the transistor from heating effect, , [Delhi PM T 2003], , (2) to enable the emitter to emit small number of, electrons and holes, (3) to enable the collector to collect 95% of the, holes or electron coming from the emitter side, (4) none of the above, In the given transistor, , C, , E, , circuit, the base, , Rb, , value of Rb is (VBE is, , IE , (4) , , IC VC, , In the study of transistor as amplifier if , , , and emitter current, then :–, , (1) 100 k, , (2) 300 k [BHU 2002], , (3) 200 k, , (4) 400 k, , In an n-p-n transistor :–, , [BHU 2002], , (3) holes move from base to collector, , 50., , (1) , , , 1, , (2) , , , 1 , , (3) , , 1, , , (4) , , 1 , , , In the CB mode of a transistor, when the collector, voltage is changed by 0.5 volt. The collector current, changes by 0.05 mA. the output resistance will be, , ce, , (4) negative charge move from collector to base, , (1) 10 k, , (2) 20 k, , iC, 0.98, iE, , (3) 5 k, , (4) 2.5 k, , ], , determine current gain of CE, , configuration :–, , 47., , 51., , Sc, i, , (1) 49, , (2) 98, , (3) 4.9, , (4) 24.5, , 52., , S, , What is the voltage gain in a common emitter amplifier, where input resistance is 3 and load resistance is, 24 :– ( = 6)?, [Delhi PM T 2000, BHU 98], (1) 2.2, , (2) 1.2, , (3) 4.8, , (4) 48, , In the circuit shown here the transistor used has, current gain = 100. What should be the base, resistor Rb so that VCE = 5V, VBE =0[Delhi PMT 2000], , Forbidden energy gap for an insulator is :–, (1) 0·1 MeV, , [AIPM T 2001], , JH, A', , 46., , [Pb. PM T 2002, Jipmer 2003], , In CB configuration of transistor ac current gain is, , en, , 45., , [Pb. PM T 2002], , Ac, , (1) holes move from emitter to base, (2) negative charge moves from emitter to base, , ic, and, ie, , ic, where ic, ib, and ie are the collector, base, ib, , y, , 7V, , assumed to negligible), , 44., , IC , (3) , , IB VC, , RL, , B, , current is 35 A. The, , 49., , IB , (2) , , IC VC, , ad, em, , 43., , IC , (1) , , IE VC, , 53., , 54., , (2) 1 keV, , [RPM T 2005], , (3) 1 eV, (4) 5 eV, A conducting wire of Copper and Germenium are, cooled from room temperature to temperature 80K,, then their resistance will :–, [RPM T 2005], (1) increase, (2) decrease, (3) copper's increase and Germenium's decrease, (4) copper's decrease and Germenium's increase, Zener dode is used for :–, [AIPM T 2005], (1) rectification, (2) stabilization, (3) amplification, (4) producing oscillations in an oscillator, Choose the only false statement from the following, [AIPM T 2005], , 1k, , Rb, , C, B, , 10V, VCE, , E, , (1) 1 × 103 , , (2) 500 , , (3) 200 × 103 , , (4) 2 × 103 , , JHA’S, Science Academy, , (1) the resistivity of a semiconductor increases with, increase in temperature, (2) substances with energy gap of the order of 10eV, are insulators, (3) in conductors the valence and conduction bands, may over lap, (4) the conductivity of a semiconductor increases, with increases in temperature, Page # 28

Page 30 :

57., , [AIIM S 2005], , 63., , (1) Above valence band, (2) Below conduction band, (3) Between valence and conduction band, (4) None of these, 62., , What is the energy gap in Si semiconductor?, [RPM T 2007], , (1) 4.4 eV, , (2) 0.3 eV, , (3) 0.7 eV, , (4) 1.1 eV, , A p–n photodiode is made of a material with a band, gap of 2.0 eV. The minimum frequency of the, , y, , (1) 1·1 mA, (2) 1·01 mA, (3) 0·01 mA, (4) 10 mA, In semiconducting material the mobilities of, electrons and holes are e and h respectively. Which, of the following is true :–, [AIIM S 2005], (1) e > h, (2) e < h, (3) e = h, (4) e < 0; h > 0, A transistor-oscillator using a resonant circuit with, an inductor L (of negligible resistance) and a, capacitor C in series produce oscillations of, frequency f. If L is doubled and C is changed to 4C,, the frequency will be :[AIPM T 2006], , Impurity energy level of n-type semi-conductor lies, in:[RPM T 2007], , radiation that can be absorbed by the material is, nearly :[AIPM T 2008], (1) 1 × 1014 Hz, , (2) 20 × 1014 Hz, (3)10 × 1014 Hz, (4) 5 × 1014 Hz, , 64., , The voltage gain of an amplifier with 9% negative, feedback is 10. The voltage gain without feedback, will be :[AIPM T 2008], , (3), , (2) 8 f, f, , (4), , 2 2, , In the energy band diagram, , JH, A', , (1) an n-type semiconductor, , 67., [AIPM T 2007], , (2) a p-type semicoductor, , (4) a metal, A common emitter amplifier has a voltage gain of, 50, an input impedance of 100 and an output, impedance of 200 . The power gain of the, amplifier is :[AIPM T 2007, 10], (1) 100, , (2) 500, , (3) 1000, , (4) 1250, , Science Academy, , (3) 90, , (4) 10, , A p-n photodiode is f abricated f rom a, , (1) 4000 Å, , (2) 6000 Å, , (3) 4000nm, , (4)6000 nm, , The device that can act as a complete electronic, circuit is :, [AIPM T 2010], (1) Zener diode, , (2) Junctions diode, , (3) Integrated circuit, , (4) Junction transistor, , Which one of the following statement is false ?, [AIPM T 2010], , (1) The resistance of intrinsic semiconductor, decreases with increase of temperature, , (3) an insulator, , JHA’S, , (2) 100, , semiconductor with a band gap of 2.5 eV. It can, detect a signal of wavelength :[AIPM T 2009], , 66., , of a material shown below,, the open circles and filled, circles denote holes and, electrons respectively. The, material is :-, , 60., , 65., , f, 2, , S, , 59., , f, 4, , (1) 1.25, , Sc, i, , (1), , en, , ce, , 58., , 61., , ad, em, , 56., , Carbon, Silicon and Germanium atoms have four, valence electrons each. Their valence and, conduction bonds are separated by energy band, gaps represented by (E g)C , (Eg)Si and (Eg)Ge, respectively. Which one of the following relationships, is true in their case :–, [AIPM T 2005], (1) (Eg)C < (Eg)Ge, (2) (Eg)C > (Eg)Si, (3) (Eg)C = (Eg)Si, (4) (Eg)C < (Eg)Si, Consider an n–p–n transistor amplifier in common–, emitter configuration. The current gain of the, transistor is 100. If the collector current changes, by 1 mA, what will be the change in emitter current, , Ac, , 55., , (2) Pure Si doped with trivalent impurities gives a, p-type semiconductor, (3) Majority carriers in a n-type semiconductor are, holes, (4) Minority carriers in a p-type semiconducrot are, electrons, Page # 29

Page 31 :

68., , A zener diode, having breakdown voltage equal to, 15 V, is used in a voltage regulator circuit shown, in figure. The current through the diode is :-, , 71., , [AIPM T(M ains) 2011], , +, , 250, , 20V, , 1k, , 15V, , –, , 72., , (1) 5 mA, , (2) 10 mA, , (3) 15 mA, , (4) 20 mA, , (2) 75, , (3) 100, , (4) 25, , In forward biasing of the p–n junction :[AIPM T(Pre.) 2011], , (1) The positive terminal of the battery is connected, to p–side and the depletion region becomes, thick, , y, , In the following figure, the diodes which are forward, biased, are :-, , (1) 50, , [AIPM T(M ains) 2011], , ad, em, , 69., , A transistor is operated in common emitter, configuration at VC = 2V such that a change in the, base current from 100 µA to 300µA produces a, change in the collector current from 10 mA to, 20 mA. The current gain is :- [AIPM T(Pre.) 2011], , +10V, , (a) +5V, , (2) The positive terminal of the battery is connected, to n-side and the depletion region becomes thin, , R, , (3) The positive terminal of the battery is connected, to n-side and the depletion region becomes, thick, , Ac, , R, (b) –10V, , ce, , –12V, , R, , 73., , en, , (c), , (4) The positive terminal of the battery is connected, to p-side and the depletion region becomes thin, , R, +5V, , 70., , (3) there will be more free electrons than holes in, the semiconductor, (4) its resistance is increased, , (2) (c) only, , JH, A', , (1) (a), (b) and (d), , (2) the antimony becomes an acceptor atom, , S, , (d), , (1) it becomes a p-type semiconductor, , Sc, i, , –5V, , (3) (c) and (a), (4) (b) and (d), Pure Si at 500 K has equal number of electron (ne), and hole (nh) concentrations to 1.5 × 1016 m–3., Doping by indium increases nh to 4.5 × 1022 m–3., The doped semiconductor is of :-, , 74., , (2) n-type with electron concentration, ne = 5 × 1022 m–3, (3) P-type with electron concentration, ne = 2.5 × 1010 m–3, (4) n-type with electron concentration, ne=2.5 × 1023 m–3, , JHA’S, Science Academy, , Direction of electric field in P-N Junction diode is:, (1) From P side to N-side, , [AIIM S 2011], , (2) From N side to P-side, (3) Randomly oriented, , [AIPM T(M ains) 2011], , (1) p-type hav ing elecron concentrations, ne = 5 × 109 m–3, , If a small amount of antimony is added to, germanium crystal :, [AIPM T(Pre.) 2011], , (4) Electric field does not exist, 75., , In a CE transistor amplifier, the audio signal voltage, across the collector resistance of 2kis 2V. If the, base resistance is 1kand the current amplification, of the transistor is 100, the input signal voltage is:[AIPM T(Pre.) 2012], , (1) 1 mV, (3) 0.1 V, , (2) 10mV, (4) 1.0 V, , Page # 30

Page 32 :

C and Si both have same lattice structure, having, 4 bonding electrons in each. However, C is insulator, where as Si is intrinsic semiconductor. This is because :, , 78., , [AIPM T(Pre.) 2012], , 77., , (1) 4000, 79., , 80., , III, , en, , ce, , II, , (3) 2000, (4) 3000, Which of the following current must be zero in an, unbiased P.N. junction diode :[AIIM S 2012], (1) Current due to majority charge carriers (both, electrons and holes), (2) Current due to minority charge carriers (both, electrons and holes), (3) Current due to majority & minority charge, carriers, (4) Current due to majority and minority charge, carriers (only holes), In the given circuit, the voltage across the load is, maintained at 12 V. The current in the zener diode, varies from 0-50 mA. What is the maximum wattage, of the diode ?, [AIIM S 2012], , Ac, , [AIPM T(Pre.) 2012], , V0 I, , Sc, i, , Vi, , 81., , JH, A', , S, , (1) in region II, (2) in region I, (3) in region III, (4) both in region (I) and (III), , (2) 1000, , y, , (1) The four bonding electrons in the case of C lie, in the second orbit, whereas in the case of Si they, lie in the third, (2) The four bonding electrons in the case of C lie, in the third orbit, whereas for Si they lie in the fourth, orbit., (3) In case of C the valance band is not completely, filled at absolute zero temperature., (4) In case of C the conduction band is partly filled, even at absolute zero temperature, Transfer characteristics (output voltage (V0) vs input, voltage (Vi ) for a base biased transistor in CE, configuration is as shown in the figure. For using, transistor as a switch, it is used., , The input resistance of a silicon transistor is 100 ., Base current is changed by 40 µA which results in, a change in collector current by 2mA. This transistor, is used as a common emitter amplifier with a load, resistance of 4 K. The voltage gain of the amplifier, is :, [AIPM T M ains 2012], , ad, em, , 76., , 20V, , (1) 12 W, (2) 6 W, (3) 0.6 W, (4) 1.2 W, For a common-emitter transistor, input current is, 5A, = 100 circuit is operated at load resistance, of 10 k then voltage across load will be :(1) 5 V, (2) 10 V [AIIM S 2012], (3) 12.5 V, (4) 7.5 V, , ANSWER KEY, Q., , 1, , Ans., , 2, , Q., , 16, , Ans., , EXERCISE - I, , 2, , 3, , 4, , 5, , 6, , 7, , 8, , 9, , 10, , 11, , 12, , 13, , 14, , 15, , 2, , 3, , 1, , 1, , 1, , 4, , 2, , 4, , 2, , 2, , 2, , 1, , 1, , 1, , 17, , 18, , 19, , 20, , 21, , 22, , 23, , 24, , 25, , 26, , 27, , 28, , 29, , 30, , 2, , 2, , 1, , 4, , 1, , 4, , 3, , 3, , 1, , 3, , 4, , 1, , 2, , 2, , 3, , Q., , 31, , 32, , 33, , 34, , 35, , 36, , 37, , 38, , 39, , 40, , 41, , 42, , 43, , 44, , 45, , Ans., , 1, , 3, , 1, , 2, , 1, , 3, , 3, , 2, , 1, , 4, , 2, , 3, , 3, , 2, , 1, , Q., , 46, , 47, , 48, , 49, , 50, , 51, , 52, , 53, , 54, , 55, , 56, , 57, , 58, , 59, , 60, , Ans., , 4, , 3, , 3, , 2, , 1, , 4, , 4, , 2, , 1, , 2, , 2, , 1, , 3, , 2, , 4, , Q., , 61, , 62, , 63, , 64, , 65, , 66, , 67, , 68, , 69, , 70, , 71, , 72, , 73, , 74, , 75, , Ans., , 2, , 4, , 4, , 2, , 1, , 3, , 3, , 1, , 3, , 1, , 1, , 4, , 3, , 2, , 2, , Q., , 76, , 77, , 78, , 79, , 80, , 81, , Ans., , 1, , 4, , 3, , 3, , 3, , 1, , JHA’S, Science Academy, , Page # 31

Page 33 :

1., , TEASERS, , EXERCISE–II, , On increasing the temperature the specific, resistance of a semiconductor :–, , 7., , A transistor is used in the common emitter mode as, an amplifier then :–, , (1) increases, , (A) the base emitter junction is forward baised, , (2) decreases, , (B) the base emitter junction is reverse baised, , (3) does not change, , (C) the input signal is connected in series with the, voltage applied to bias the base emitter junction, , (4) first decreases and then increases, 2., , Platinum and silicon are cooled after heating up to, 2500 C. :–, , (D) the input signal is connected in series with the, voltage applied to bias the base collector, junction, , (1) resistance of platinum will increase and that of, silicon decreases, , (3) resistance of both will decreas, , 4., , 8., , (4) only C, , When a potential difference is applied across, the, current passing through :–, , The atomic bonding is same for which of the following, pairs :–, , (1) a semiconductor at 0K is zero, , (1) Ag and Si, , (2) Ge and Si, , (2) a metal at 0K is finite, , (2) Ne and Ge, , (4) Nacl and Ge, , (3) a P-N diode at 300K is finite if it is reverse, biased, , Which of the following energy band diagram shows, the N-type semiconductor :–, , (4) all, , (3), , en, , JH, A', , Valence, Band, , Valence, Band, , Sc, i, , Valence, Band, , Impurity level, 1 eV, Conduction, Band, , (2) 25, , (3) both electrons and holes, (4) neither electrons nor holes, 10., , Valence, Band, , (3) v will increase but n will decrease, (4) both n and v will decrease, , Conduction, Band, , (3) 2.5, , 11., , Let np and ne be the numbers of holes and, conduction electrons in an extrinsic semiconductor., (1) np > ne, (3) np < ne, , (4) 35, , In a P–N Junction diode not connected to any circuit, (1) potential is the same every where, , An electric field is applied to a semiconductor. Let, the number of charge carriers density is 'n' and the, average drift speed be v. If the temperature is, increased :–, (1) both n and v will increase, (2) n will increase but v will decrease, , (4) 1 eV Impurity level, , Which value of potential barrier is in the range, for, given PN junction :–, (1) 0.2, , Electric conduction in a semiconductor takes place, due to :–, (1) electrons only, (2) holes only, , Impurity level, 1, eV, (2), , S, , E=1eV, g, , (1), , Conduction, Band, , ce, , 9., , 6., , (3) A, C, , (4) resistance of both increases, , Conduction, Band, , 5., , (2) A, D, , Ac, , 3., , (1) A, B, , ad, em, , (2) resistance of silicon will increase and that of, platinum decreases, , y, , BRAIN, , 12., , A p-type semiconductor is :–, , (2) the P - type side is at a higher potential than the, n - type side, , (1) positively charged, , (3) there is an electric field at the junction directed, form the n - type side to the P - type side, , (3) uncharged, , (4) there is an electric field at the junction directed, form the P - type side to the n - type side, , JHA’S, Science Academy, , (2) np = ne, (4) np ne, , (2) negatively charged, (4) uncharged at 0K but charged at higher, temperatures, , Page # 32

Page 34 :