Notes of Msc Sem 4 Microprocessor, Microprocessor 8085 notes sem 4s.pdf - Study Material

Page 2 :

INDEX, CHAPTER 1, 1.1, 1.2, 1.3, 1.4, 1.5, 1.6, , Introduction to Microprocessor, Microprocessor architecture and its operations, Memory, Input & output devices, Logic devices for interfacing, The 8085 MPU, Example of an 8085 based computer, Memory interfacing, , 2.1, 2.2, 2.3, 2.4, 2.5, 2.6, 2.7, 2.8, 2.9, 2.10, 2.11, , CHAPTER 2, Basic interfacing concepts, Interfacing output displays, Interfacing input devices, Memory mapped I/O, Flow chart symbols, Data Transfer operations, Arithmetic operations, Logic Operations, Branch operation, Writing assembly language programs, Programming techniques: looping, counting and indexing, , 3.1, 3.2, 3.3, 3.4, 3.5, 3.5.1, 3.5.2, 3.5.3, 3.5.4, 3.6, 3.7, 3.8, 3.9, 3.9.1, , CHAPTER 3, Additional data transfer and 16 bit arithmetic instruction, Arithmetic operations related to memory, Logic operation: rotate, compare, Counter and time delays, Illustrative program, Hexadecimal counter, zero-to-nine, (module ten) counter, Generating pulse waveforms, Debugging counter and time delay, Stack, Subroutine, Restart, Conditional call and return instructions, Advance subroutine concepts, The 8085 Interrupts, 8085 vector interrupts., , CHAPTER 4, , 3

Page 3 :

4.1, 4.2, 4.3, 4.4, 4.5, 4.6, 4.7, , BCD-to-Binary conversion, Binary-to-BCD conversion, BCD-to-Seven segment code converter, Binary-to-ASCII, ASCII-to-Binary code conversion, BCD Addition, BCD Subtraction, , 4.8, 4.9, , Introduction to Advance instructions and Application, Multiplication, Subtraction with carry, , 5.1, 5.2, 5.3, 5.4, 5.5, 5.6, 5.7, , CHAPTER 5, 8255 Programmable peripheral interface, interfacing keyboard and seven segment display,, 8254 (8253) programmable interval timer,, 8259A programmable interrupt controller,, Direct Memory Access and 8237 DMA controller., Introduction to 8086 microprocessor: Architecture of 8086, Pin diagram, Functional block diagram, Register organization., , 3

Page 4 :

UNIT 1, 1.1, INTRODUCTION TO MICROPROCESSOR: Microprocessors are regarded as, one of the most important devices in our everyday machines called computers. Before we start, we, need to understand what exactly microprocessors are and their appropriate implementations., Microprocessor is an electronic circuit that functions as the central processing unit (CPU) of a, computer, providing computational control. Microprocessors are also used in other advanced, electronic systems, such as computer printers, automobiles, and jet airliners Typical microprocessors, incorporate arithmetic and logic functional units as well as the associated control logic, instruction, processing circuitry, and a portion of the memory hierarchy. Portions of the interface logic for the, input/output (I/O) and memory subsystems may also be infused, allowing cheaper overall systems., While many microprocessors and single-chip designs, some high- performance designs rely on a few, chips to provide multiple functional units and relatively large caches. When combined with other, integrated circuits that provide storage for data and programs, often on a single semiconductor base, to form a chip, the microprocessor becomes the heart of a small computer, or microcomputer., Microprocessors are classified by the semiconductor technology of their design (TTL, transistortransistor logic; CMOS, complementary-metal-oxide semiconductor; or ECL, emitter-coupled logic),, by the width of the data format (4-bit, 8-bit, 16-bit, 32-bit, or 64-bit) they process; and by their, instruction set (CISC, complex-instruction-set computer, or RISC, reduced-instruction-set computer;, see RISC processor). TTL technology is most commonly used, while CMOS is preferred for portable, computers and other battery-powered devices because of its low power consumption. ECL is used, where the need for its greater speed offsets the fact that it consumes the most power. Four-bit devices,, while inexpensive, are good only for simple control applications; in general, the wider the data format,, the faster and more expensive the device. CISC processors, which have 70 to several hundred, instructions, are easier to program than RISC processors, but are slower and more expensive., Microprocessors have been described in many different ways. They have been compared with the, brain and the heart of humans. Their operation has been likened to a switched board, and to the, nervous system in an animal. They have often been called microcomputers. The original purpose of, the microprocessor was to control memory. That is what they were originally designed to do, and, that is what they do today. Specifically, a microprocessor is “a component that implements memory., A microprocessor can do any information-processing task that can be expressed, precisely, as a plan., It is totally uncommitted as to what its plan will be. It is a truly general-purpose informationprocessing device. The plan, which it is to execute—which will, in other words, control its, operation—is stored electronically. This is the principle of “stored program control”. Without a, program the microprocessor can do nothing. With one, it can do anything. Furthermore,, microprocessors can only perform information-processing tasks. To take action on the outside, world, or to receive signals from it, a connection must be provided between the microprocessor’s, representation of information (as digital electronic signals) and the real world representation., 4-BIT MICROPROCESSORS:, Historically, the 4-bit microprocessor was the first general-purpose microprocessor introduced on the, market. The basic design of the early microprocessors was derived from that of the desk

Page 5 :

calculator. The Intel 4004, a 4-bit design, was t4he grandfather of microprocessors. Introduced in, late 1971, the 4004 was originally designed for a Japanese manufacturer as the processing element of, a desk calculator; it was not designed as a general-purpose computer. The shortcomings of the 4004, were recognized as soon as it was introduced. But it was the first general-purpose computing device, on a chip to be placed on the market. Many of the chips introduced at about the same time by other, companies were, in fact, mere calculator chips. Some of them were even serial-by-bit devices, which, performed calculations a single bit at a time. The Intel 4004 chip took the integrated circuit down, one step further by placing all the parts that made a computer think (i.e. central processing unit,, memory, input and output controls) on one small chip. Programming intelligence into inanimate, objects had now become possible. The 4004 was the world's first universal microprocessor. In the, late 1960s, many scientists had discussed the possibility of a computer on a chip, but nearly everyone, felt that integrated circuit technology was not yet ready to support such a chip. Intel's Ted Hoff felt, differently; he was the first person to recognize that the new silicon-gated MOS technology might, make a single-chip CPU (central processing unit) possible., , 8-BIT MICROPROCESSORS:, Today, 8-bit microprocessors coexist with 16-bit microprocessors as the design standard. Although 16bit chips provide higher performance computationally, 8-bit designs have more than adequate power, for many applications—plus the advantage of lower cost. As originally design, most 16-bit, microprocessors were limited to packages with a maximum of 40 to48 pins. This was not due to, physical, but rather to economic, constraints: industrial tester of the time was generally limited to 40pin DIPs. The ancestor of today’s 8-bit microprocessors was the Intel 8008, introduced in 1972- 1973., The 8008 was not intended to be a general-purpose microprocessor. IT was to be a CRT display, controller for Data point. Taking into account all of its design inadequacies and its limited, performance, the 8008 was an overwhelming success. (Bernstein, p.202), INTEL (8-BIT MICROPROCESSORS) :, The 8080, designed as a successor to Intel’s 8008, was the first powerful microprocessor introduced, on the market. Several other microprocessors of similar performance were introduced on the market, within a year after the 8080 appeared, and several additional powerful designs were introduced later., Technically, however, the 8080 long remained the most powerful product on the market., Furthermore, Intel was the first company to invest in the development of support chips and software, for its products. This ensured the continued success of the 8080 because its performance was then, sufficient for many applications. The early 8080 competitors were introduced with at least a ninemonth delay and failed to dislodge it. The 8080 is still sold today thought It has been largely eclipsed, by successor products—most notably the 8085 microprocessor. Today, the 8085 accounts for roughly, one of every four 8-bit microprocessors sold., 1.2, MICROPROCESSOR ARCHITECTURE AND ITS OPERATION:, Computer system consist primary of :1- Microprocessor., 2-Memory., 3-Input., 4-Output., The internal logic design of the microprocessor called its"architecture", determine how and, what various operations are performed by "MICROPROCESSOR"., Microprocessor architecture and its operations: The microprocessor is programmable logic, device designed with register,flip-flop and timing elements., All function performed by microprocessor can by classified in three general categories:-1-

Page 6 :

Microprocessor initiated operations., 2- Internal data operations., 3- Peripheral (or externally) initiated operations., To performed these operations, microprocessor needs [logic circuit and control signals]., 1- Microprocessor Initiated Operations:Primarily microprocessor performs four operations:a) Memory read (Reads data from memory)., b) Memory writes (Write data into memory)., c) I/O read (Accept data to output device)., d) I/O writes (Sends data to output device)., These operation are part of communication process., Microprocessor performed these functions using sets of buses [Data bus, Address bus, Control, bus]., Data bus: - is a group of 8 lines used for data flow, these lines are bidirectional from (00 – FF) =28, =256 numbers. The largest number = 1111 1111 = FF , thus 8085 Microprocessor is called 8bit, Microprocessor., Address bus: - is a group of 16 lines, identified as 0 – 15. This bus is unidirectional (bit flow in, one direction) from Microprocessor to peripheral. Each memory location or peripheral identified, with binary number called address. (216 =65536=64K)., Control bus: - the control is comprised of various single lines that carry synchronization signals., , Fig. 1.1 The 8085 Bus System, The microprocessor needs to perform the followingsteps:i) Identify the peripheral (memory location)., ii) Transfer data., iii) Provide timing or synchronization signals., 2- Internal Data Operations:The internal architecture of the 8085/8080A microprocessor determines how and what operation can, be performed with the data. These operations are:-

Page 7 :

Store 8-bit data., , Performed arithmetic and logical operations. Test for conditions.Sequence the, , execution of instructions. Store data temporarily during execution in the defined R/W memory, locations called the stack.To perform these operations the Microprocessor requires:a) Registers., b) An arithmetic logic unit (ALU) & control logic., c) Internal buses (paths for information flow)., Fig1.2 : The 8085 Programmable Register, , 3- Peripheral or Externally Initiated Operations:External devices (or signals) can initiate the following operation for which individual pins on, Microprocessor chip are assigned: Reset, Interrupt, Ready, Hold., A), Reset: when reset is activated all internal operations are suspended and the program counter, iscleared., B), Interrupt: the Microprocessor can be interrupted from normal execution and asked to, execute other instructions called "service routine" (emergency), Microprocessor resumes its, operation after that., C), Ready: 8085 has pin called ready, if the signal is low Microprocessor enters into wait state,, thissignal used to synchronized slower peripherals with Microprocessor., D), Hold: when hold pin activated by external signal Microprocessor relinquishes control buses, and allows the external peripheral to use the. For example: Hold signal is used in direct memory, accessdata transfer., 1.3, MEMORY, INPUT AND OUTPUT: Memory is an essential component of a, microprocessor system; it stores binary information. The memory is made up of semiconductor, material used to store the programs and data. The types of memory is, Primary or main memory and, Secondary memory., Primary memory: RAM and ROM are examples of this type of memory. Microprocessor uses it in, storing a program temporarily (commonly called loading) and executing a program. Hence the speed, of this type of memory should be fast.

Page 8 :

Secondary memory: These are used for bulk storage of data and information. The main examples, include Floppy, Hard Disk, CD-ROM, Magnetic Tape etc. Slower and Sequential Access, Nature.non-volatile nature., , Fig. 1.3 Memory chip, The Basic Memory Element: The basic memory element is similar to a D latch.This latch has an, input where the data comes in. It has an enable input and an output on which data comes out., , Fig. 1.4 D Latch, , Fig.1.5: D latch as a 4-bit storage element, Address Decoding and Memory Mapping: Memory address decoding is nothing but to assign an, address for each location in the memory chip. The data stored in the memory is accessed by

Page 9 :

specifying its address. Memory address can be decoded in two ways:, i)Absolute or Fully decoding and ii) Linear Select or Partial decodingThere are many advantages in, absolute address decoding., i), ii), , Each memory location has only one address, there is no duplication in the address, Memory can be placed contiguously in the address space of the microprocessor., i) Future expansion can be made easily without disturbing the existing circuitryThere are few, disadvantages in this method., Extra decoders are necessary, ii) Some delay will be produced by these extra decoders., The main advantage of linear select decoding is its simplified decoding circuit.This reduces the, hardware design cost. But there are many disadvantages in this decoding., i) Multiple addresses are provided for the same location, ii) Complete memory space of the microprocessor is not efficiently used, iii) Adding or interfacing ICs with already existing circuitry is difficult., Absolute Address Decoding: The 8085 microprocessor has 16 address lines. Therefore it can access 216, locations in the physical memory. If all these lines are connected to a single memory device, it will, decode these 16 address lines internally and produces 216 different addresses from 0000H to FFFFH, so that each location in the memory will have a unique address., , Fig. 1.6 Memory Address, Above diagram shows the various memory addresses used in Microprocessor. If more than one chips, are used then some logic must be used to select one particular chip. This is done with the help of, decoder., 74LS138 address decoder to generate the chip select signals for eachmemory block. In this decoder, when the address lines A13, A14 and A15 are 000, theoutput lineY0 will be activated as shown in Fig, 1.7. This in turn selects the firstmemory block. Similarly when these lines are 001 (C=0, B=0 and, A=1) Y1 will beactivated and the second memory block will be selected.

Page 10 :

Fig 1.7: Memory block decoder, In this type of memory interfacing, all the address lines (A0 to A15) have beenused. Each location in, the memory will have a single address. This type of addressdecoding is called as absolute or fully, decoded addressing., , Fig. 1.8: Role of CS signal, According to the value of Ao and A1 , any one register will be selected and to select one memory, chip we need one chip select signal CS signal as shown in the next diagram., If CS’ is ‘0’memory 1 will be selected else memory2 will be selected. And the complete picture of the

Page 11 :

interfacing is shown below. Fig. 1.9: The complete interfacing diagram, The simple view of RAM is that it is made up of registers that are made up of flip-flops (or memory, elements). The number of flip-flops in a “memory register” determines the size of the memory, word.ROM on the other hand uses diodes instead of the flip-flops to permanently hold the, information. For the microprocessor to access (Read or Write) information in memory (RAM or, ROM), it needs to do the following:, Select the right memory chip (using part of the address bus). Identify the memory location (using the, rest of the address bus). Access the data (using the data bus)., , Fig. 1.10 Memory Interface Diagram, Tri-State Buffers: An important circuit element that is used extensively in memory. This buffer is a, logic circuit that has three states: Logic 0, logic1, and high impedance. When this circuit is in high, impedance mode it looks as if it is disconnected from the output completely. This circuit has two, inputs and one output. The first input behaves like the normal input for the circuit. The second input is, an “enable”. If it is set high, the output follows the proper circuit behaviour. If it is set low, the output, looks like a wire connected to nothing., Input /Output Devices: Parallel Interfacing: There are two ways to interface 8085 with I/O devices, in parallel data transfer mode: Memory Mapped IO and IO mapped IO., Memory mapped I/O: It considers them like any other memory location. They are assigned a 16-bit, address within the address range of the 8085.The exchange of data with these devices follows the, transfer of data with memory. The user uses the same instructions used for memory., I/O mapped I/O: It treats them separately from memory: I/O devices are assigned a “port number”, within the 8-bit address range of 00H to FFH. The user in this case would access these devices using, the IN and OUT instructions only.

Page 12 :

IO mapped IO V/s Memory Mapped IO:, , Memory Mapped IO, , IO mapped IO, , •, , IO is treated as memory., , •, , IO is treated IO., , •, , 16-bit addressing., , •, , 8- bit addressing., , •, , More Decoder Hardware., , •, , Less Decoder Hardware., , •, , Can address 216=64k locations., , •, , Can address 28=256 locations., , •, , Less memory is available., , •, , Whole memory address space is available., , •, , Memory Instructions are used., , •, , Special Instructions are used like IN, OUT., , •, , Memory control signals are used., , •, , Special control signals are used., , •, , Arithmetic and logic operations can be, performed on data., , •, , Arithmetic and logic operations cannot be, performed on data., , •, , Data transfer b/w register and IO., , •, , Data transfer b/w accumulator and IO., , 1.4, LOGIC DEVICES FOR INTERFACING: Several types of interfacing devices are, necessary to interconnect the components of a bus oriented system. Tristate logic devices are, essential to proper functioning of bus oriented system., Tri state Devices: A tri state (bus driver) device is a device that can be active low, active high, or, floating. The use of a tri state device is that several of them can be connected to a single bus line, and, so long as only one of them is non-floating, the bus line can be driven by multiple senders. The, data bus is most often implemented with tri state drivers., , Fig.1.11 Tri state device, The data will be passed to the output terminal whenever the OE terminal is activated, else the device, will be in high impedance state.

Page 13 :

Fig.1.12 Octal 3 state Buffer, It is common to use an octal 3-state buffer as shown in fig. 1.12 to create a byte-wide input port. The, ‘541 has dual active-low enable inputs in order to pass its D inputs from input devices to their, respective Q outputs and onto the system data bus. OE1 could connect to the address decoder for, this input port while OE2 could connect to an active-low READ strobe. This READ strobe, requirement is imperative so as to keep the output drivers disabled and avoid the dreaded “self, destruct state” due to bus contention. Bus contention is the result of more than a single driver on a, shared bus line being active at the same time and potentially driving a bus line to opposing logic, levels. Such would be the case if the READ strobe were ignored during a CPU write operation., Bidirectional Ports: The octal bus transceivers are designed for asynchronous two-way, communication between data buses. The control-function implementation minimizes external timing, requirements., The devices allow data transmission from the A bus to the B bus or from the B bus to the A bus,, depending on the logic level at the direction-control (DIR) input. The output-enable (OE)\ input can, disable the device so that the buses are effectively isolated., Features, , , 3-State Outputs Drive Bus Lines Directly, , , , PNP Inputs Reduce dc Loading on Bus Lines, , , , Hysteresis at Bus Inputs Improves Noise Margins, , , , Typical Propagation Delay Times Port to Port, 8 ns, IC used for this purpose is 74LS245 and the pin diagram is shown below:

Page 14 :

Fig. 1.13 Logic diagram and function Table of 74LS245 Bidirectional buffer, D-Latch: Latch and flip flop are the most common logic devices that are used to store one bit data. A, simple latch has two stable logic states. The latch maintains its states indefinitely until an input pulse, called a trigger is received. If a trigger is received, the latch outputs change states according to, defined rules, and remain in those states until another trigger is received. Latches can be, interconnected to form more sophisticated circuits that function in memory chips, and microprocessors., An octal latch can hold onto the data at its inputs before transmitting the data to its outputs. This, ability is useful in applications where a number of devices share a single data bus, because it allows the, processor to store data, go onto other operations that require the bus, and return to the stored data, later if the need arises., And the group of latch or flip flop is known as register. Commonly used IC is 74LS373. Pin diagram, is shown below., Fig1.14 Pin Diagram of 74LS373

Page 15 :

1.5, 8085 MPU: The microprocessor is a semiconductor device (Integrated Circuit), manufactured by the VLSI (VeryLarge Scale Integration) technique. It includes the ALU, register, arrays and control circuit on asingle chip. To perform a function or useful task we have to form a, system by using microprocessor as a CPU and interfacing memory, input and output devices to it. A, system designed using a microprocessor as its CPU is called a microcomputer. The Microprocessor, based system (single board microcomputer) consists of microprocessor as CPU, semiconductor, memories like EPROM and RAM, input device, output device and interfacing devices. The, memories, input device, output device and interfacing devices are called peripherals. The popular, input devices are keyboard and floppy disk and the output devices are printer, LED/LCD displays, CRT, monitor, etc, The main features of 8085 μp are:, •, It is a 8 bit microprocessor., •, it is manufactured with N-MOS technology., •, It has 16-bit address bus and hence can address up to 216 = 65536 bytes (64KB) memory, locationsthrough A0-A15, • The first 8 lines of address bus and 8 lines of data bus are multiplexed AD0 – AD7, • Data bus is a group of 8 lines D0 – D7, • It supports external interrupt request. ., • A 16 bit program counter (PC), • A 16 bit stack pointer (SP), • Six 8-bit general purpose register arranged in pairs: BC, DE, HL., • It requires a signal +5V power supply and operates at 3.2 MHZ single phase clock., • It is enclosed with 40 pins DIP (Dual in line package).

Page 16 :

Fig.1.15 Pin diagram of 8085 Microprocessor, System Bus: Typical system uses a number of busses, collection of wires, which transmit binary, numbers, one bit per wire. A typical microprocessor communicates with memory and other devices, (input and output) using three busses: Address Bus, Data Bus and Control Bus., Address Bus :One wire for each bit, therefore 16 bits = 16 wires. Binary number carried alerts, memory to ‘open’ the designated box. Data (binary) can then be put in or taken out. The Address, Bus consists of 16 wires, therefore 16 bits. Its "width" is 16 bits. A 16 bit binary number allows 216, different numbers, or 32000 different numbers, ie 0000000000000000 up to 1111111111111111., Because memory consists of boxes, each with a unique address, the size of the address bus, determines the size of memory, which can be used. To communicate with memory the, microprocessor sends an address on the address bus, eg 0000000000000011 (3 in decimal), to the, memory. The memory the selects box number 3 for reading or writing data. Address bus is, unidirectional, ie numbers only sent from microprocessor to memory, not other way. These address, lines are split into two parts A15-A8 are unidirectional and AD0-AD7.

Page 17 :

Fig 1.16: Address bus and Data bus, Data Bus: Data buses used to transfer instructions and data.8085 has a 8-bit data bus, Demultiplexing Address/Data Lines: 8085 identifies a memory location with its 16 address lines,, (AD0 to AD7) & (A8 to A15) .8085 performs data transfer using its data lines, AD0 to AD7.Lower, order address bus & Data bus are multiplexed on same lines i.e. AD0 to AD7.Demultiplexing refers, to separating Address & Data signals for read/write operations., , Fig. 1.17 Need for Demultiplexing, Fig 1.17: Demultiplexing data lines from address lines, , Control and Status signal: This group of signals includes two control signals (RD and WR), three, status signals (IO/M, S1 and S0) to identify the nature of the operation. These signalsare as follows:

Page 18 :

ALE (Address Latch Enable): This is a positive going pulse generated every time the 8085 begins an, operation (machine cycle); it indicates that the bits on AD7-AD0 are address bits. This signal is used, primarily to latch the low-order address from the multiplexed bus and generate a separate set of eight, address lines, A7-A0., RD (Read): This is a Read control signal (Active Low). This signal indicates that the selected I/O or, memory device is to be read and data are available on the data bus., WR (Write): This is a write control signal (Active Low). This signal indicates that the data on the, data bus are to be written into a selected memory or I/O location., IO/M: This is a status signal used to differentiate between I/O and memory operations. When it is, high, it indicates an I/O operation: when it is low, it indicates a memory operation. This signal is, combined with RD (read) and WR (Write) to generate I/O and memory control signals., S1 and S0: These status signals, similar to IO/M, can be identify various operations, but they are, rarely used in small systems., Power Supply and Clock frequency: The power supply and frequency that are used in 8085, Microprocessor are as follow:, Vcc: +5V power supply.Vss: Ground reference., X1, X2: A crystal is connected at these two pins. The frequency is internally divided by two;, therefore, to operate a system at a 3 MHz, the crystal should have a frequency of 6 MHz ., CLK (OUT)-Clock Output: This signal can be used as the system clock for other devices., Pin description: Properties : Single + 5V Supply , 4 Vectored Interrupts (One is Non Maskable) ,, Serial In/Serial Out Port , Decimal, Binary, and Double Precision Arithmetic . Direct Addressing, Capability to 64K bytes of memory, The Intel 8085A is a new generation, complete 8 bit parallel central processing unit (CPU). The, 8085A uses a multiplexed data bus. The address is split between the 8bit address bus and the 8bit, data bus. Figures are at the end of the document., Pin Description : The following describes the function of each pin:, A6 - A1s (Output 3 State), Address Bus; The most significant 8 bits of the memory address or the 8 bits of the I/0 address,3, stated during Hold and Halt modes., AD0 - 7 (Input/Output 3state) :Multiplexed Address/Data Bus; Lower 8 bits of the memory address (or, I/0 address) appear on the bus during the first clock cycle of a machine state. It then becomes the, data bus during the second and third clock cycles. 3 stated during Hold and Halt modes., ALE (Output) : Address Latch Enable: It occurs during the first clock cycle of a machine state and, enables the address to get latched into the on ch1ip9 latch of peripherals. The falling edge of ALE is set

Page 19 :

to guarantee setup and hold times for the address information. ALE can also be used to strobe the, status information. ALE is never 3stated., SO, S1 (Output), Data Bus Status. Encoded status of the bus cycle:, S1, , S0, , Operation, , O, , O, , HALT, , 0, , 1, , WRITE, , 1, , 0, , READ, , 1, , 1, , FETCH, , S1 can be used as an advanced R/W status., RD (Output 3state) : READ; indicates the selected memory or 1/0 device is to be read and that the, Data Bus is available for the data transfer., WR (Output 3state) : WRITE; indicates the data on the Data Bus is to be written into the selected, memory or 1/0 location. Data is set up at the trailing edge of WR. 3stated during Hold and Halt, modes., READY (Input) :If Ready is high during a read or write cycle, it indicates that the memory or, peripheral is ready to send or receive data. If Ready is low, the CPU will wait for Ready to go high, before completing the read or write cycle., HOLD (Input) :HOLD; indicates that another Master is requesting the use of the Address and Data, Buses. The CPU, upon receiving the Hold request. will relinquish the use of buses as soon as the, completion of the current machine cycle. Internal processing can continue., The processor can regain the buses only after the Hold is removed. When the Hold is acknowledged,, the Address, Data, RD, WR, and IO/M lines are 3stated., HLDA (Output) :HOLD ACKNOWLEDGE; indicates that the CPU has received the Hold request, and that it will relinquish the buses in the next clock cycle. HLDA goes low after the Hold request is, removed. The CPU takes the buses one half clock cycle after HLDA goes low., INTR (Input) :INTERRUPT REQUEST; is used as a general purpose interrupt. It is sampled only, during the next to the last clock cycle of the instruction. If it is active, the Program Counter (PC), will be inhibited from incrementing and an INTA will be issued. During this cycle a RESTART or, CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and, disabled by software. It is disabled by Reset and immediately after an interrupt is accepted., INTA (Output) :INTERRUPT ACKNOWLEDGE; is used instead of (and has the same timing as) RD, during the Instruction cycle after an INTR is accepted. It can be used to activate the 8259 Interrupt

Page 20 :

chip or some other interrupt port., RST 5.5, RST 6.5 - (Inputs), RST 7.5, RESTART INTERRUPTS; These three inputs have the same timing as I NTR except they cause an, internal RESTART to be automatically inserted. RST 7.5 ~~ Highest Priority, RST 6.5 RST 5.5 o Lowest Priority .The priority of these interrupts is ordered as shown above., These interrupts have a higher priority than the INTR., TRAP (Input): Trap interrupt is a nonmaskable restart interrupt. It is recognized at the same time as, INTR. It is unaffected by any mask or Interrupt Enable. It has the highest priority of any interrupt., RESET IN (Input) :Reset sets the Program Counter to zero and resets the Interrupt Enable and, HLDA flipflops. None of the other flags or registers (except the instruction register) are affected The, CPU is held in the reset condition as long as Reset is applied., RESET OUT (Output) :Indicates CPlJ is being reset. Can be used as a system RESET. The signal is, synchronized to the processor clock., X1, X2 (Input) :Crystal or R/C network connections to set the internal clock generator X1 can also be, an external clock input instead of a crystal. The input frequency is divided by 2 to give the internal, operating frequency., CLK (Output) :Clock Output for use as a system clock when a crystal or R/ C network is used as an, input to the CPU. The period of CLK is twice the X1, X2 input period., IO/M (Output) :IO/M indicates whether the Read/Write is to memory or l/O Tristated during Hold, and Halt modes., SID (Input) :Serial input data line The data on this line is loaded into accumulator bit 7 whenever a, RIM instruction is executed., SOD (output) :Serial output data line. The output SOD is set or reset as specified by the SIM, instruction., Generating Control signals: The Mp provides RD and WR signals to initiate read and write cycle., Because these signals are used both for reading / writing memory or reading writing an input/output, device, it is necessary to generate separate read and write signals for memory and I/O devices. 8085, provides IO/M signal to indicate that initiated cycle is for I/O device or for memory device. Using, IO/M signal along with RD and WR, it is possible to generate four signals shown below.

Page 21 :

Fig.1.18 : Generating Control SignalsGenerationof control signals:, Table 1.2: Generation of control signals, , 8085 Block Diagram: The functional block diagram or architecture of 8085 Microprocessor is very, important as it gives the complete details about a Microprocessor. Fig. shows the Block diagram of a, Microprocessor.

Page 22 :

8085 Bus Structure:, Address Bus:The address bus is a group of 16 lines generally identified as A0 to A15., The address bus is unidirectional: bits flow in one direction-from the MPU to peripheral devices.The, MPU uses the address bus to perform the first function: identifying a peripheral or a memory, location., Fig. 1.19: Block Diagram of 8085 Microprocessor, Data Bus: The data bus is a group of eight lines used for data flow. These lines are bi-directional data flow in both directions between the MPU and memory and peripheral devices. The MPU uses the, , data bus to perform the second function: transferring binary information. The eight data lines enable, the MPU to manipulate 8-bit data ranging from 00 to FF (28 = 256 numbers).The largest number, that can appear on the data bus is 11111111., Control Bus: The control bus carries synchronization signals and providing timing signals. The, MPU generates specific control signals for every operation it performs. These signals are used to, identify a device type with which the MPU wants to communicate., Registers of 8085:The 8085 have six general-purpose registers to store 8-bit data during program, execution.These registers are identified as B, C, D, E, H, and L.They can be combined as register, pairs-BC, DE, and HL-to perform some 16-bit operations., Accumulator (A):, , , , The accumulator is an 8-bit register that is part of the arithmetic/logic unit (ALU)., This register is used to store 8-bit data and to perform arithmetic and logical operations., The result of an operation is stored in the accumulator., ,

Page 23 :

Flags:, , , , , The ALU includes five flip-flops that are set or reset according to the result of an operation., The microprocessor uses the flags for testing the data conditions., They are Zero (Z), Carry (CY), Sign (S), Parity (P), and Auxiliary Carry (AC) flags. Themost, commonly used flags are Sign, Zero, and Carry., The bit position for the flags in flag register is,, , Fig.1.20 Flag register, 1. Sign Flag (S): After execution of any arithmetic and logical operation, if D7 of the result is 1, the sign, flag is set. Otherwise it is reset.D7 is reserved for indicating the sign; the remaining is the magnitude, of number. If D7 is 1, the number will be viewed as negative number. If D7 is 0, the number will be, viewed as positive number., 2. Zero Flag (z): If the result of arithmetic and logical operation is zero, then zero flag is set otherwise, it is reset., 3. Auxiliary Carry Flag (AC): f D3 generates any carry when doing any arithmetic and logical, operation, this flag is set. Otherwise it is reset., 4. Parity Flag (P): If the result of arithmetic and logical operation contains even number of 1's then this, flag will be set and if it is odd number of 1's it will be reset., 5. Carry Flag (CY):If any arithmetic and logical operation result any carry then carry flag is set, otherwise it is reset., Arithmetic and Logic Unit (ALU):It is used to perform the arithmetic operations like addition,, subtraction, multiplication, division, increment and decrement and logical operations like AND, OR, and EX-OR.It receives the data from accumulator and registers. According to the result it set or reset, the flags., Program Counter (PC): This 16-bit register sequencing the execution of instructions. It is a memory, pointer. Memory locations have 16-bit addresses, and that is why this is a 16-bit register. The, function of the program counter is to point to the memory address of the next instruction to be, executed. When an opcode is being fetched, the program counter is incremented by one to point to the, next memory location., Stack Pointer (Sp): The stack pointer is also a 16-bit register used as a memory pointer. It points to a, memory location in R/W memory, called the stack. The beginning of the stack is defined by loading, a 16-bit address in the stack pointer (register)., Temporary Register: It is used to hold the data during the arithmetic and logical operations., , , Instruction Register: When an instruction is fetched from the memory, it is loaded in the instruction, register.

Page 24 :

, , Instruction Decoder: It gets the instruction from the instruction register and decodes the, , , , Serial I/O Control: It has two control signals named SID and SOD for serial datatransmission., Timing and Control unit., , , , It has three control signals ALE, RD (Active low) and WR (Active low) and three statussignals, IO/M(Active low), S0 and S1., , , , ALE is used for provide control signal to synchronize the components of microprocessor and timing, for instruction to perform the operation., , , , RD (Active low) and WR (Active low) are used to indicate whether the operation is readingthe data, from memory or writing the data into memory respectively., , , , IO/M(Active low) is used to indicate whether the operation is belongs to the memory or, peripherals., Table 1.3 Machine cycle status and control signals, , 1.5.1The 8085 machine cycles and bus timings: Introduction: A machine cycle is the time required, to complete one operation of accessing the memory, I/O or acknowledge an external signal or request., Usually machine cycle consists of 3 to 6 T-states. In this article let us discuss about their different, types and how they are being classified., Types of machine cycle, There are various types of machine cycles which are classified based onStatus signals (IO/M’, S1, and S0) ,Control Signals (RD’, WR’, INTA)., The different types of machine cycle available in 8085 microprocessor are: Opcode Fetch, Memory ReadMemory writeI/O Read, I/O Write

Page 25 :

INTR AcknowledgeBus Idle, Table 1.4: 8085 machine cycle status and control signals, , Opcode fetch machine cycle: The Opcode fetch cycle, fetches the instructions from memory and, delivers it to the instruction register of the microprocessor. For any instruction cycle, Opcode fetch is, the first machine cycle. We know that each machine cycle may have 3 to 6 T-states. This Opcode fetch, machine cycle consists of 4 T-states., T1 State: During the T1 state, the contents of the program counter are placed on the 16 bit address, bus. The higher order 8 bits are transferred to address bus (A8-A15) and lower order 8 bits are, transferred to multiplexed A/D (AD0-AD7) bus., After the address bits are transferred, the ALE (address latch enable) signal goes high. As soon as, ALE goes high, the memory latches the AD0-AD7 bus. At the middle of the T state the ALE goes, low and the complete 16-bit address is made available for the Opcode fetch machine cycle., T2 State: During the beginning of this state, the RD’ signal goes low to enable memory. It is during, this state, the selected memory location is placed on D0-D7 of the Address/Data multiplexed bus., T3 State: In the previous state the Opcode is placed in D0-D7 of the A/D bus. In this state of the, cycle, the Opcode of the A/D bus is transferred to the instruction register of the microprocessor., Now the RD’ goes high after this action and thus disables the memory from A/D bus., T4 State: In this state the Opcode which was fetched from the memory is decoded., Thus the cycle completes after 4 T-states. This very well explains the Opcode fetch machine cycle. For, better understanding of the concept, a diagram explaining Opcode fetch cycle is shown below., , 26

Page 26 :

Fig 1.21 Memory Read machine cycle, If the instruction is only one byte in length, then one machine cycle is enough to complete the, process (Opcode fetch cycle). When the instruction has more than one byte of information to be, processed, then the microprocessor may require more than one machine cycle to complete the, process. The machine cycle in this case would require reading of address or data from memory or, any other I/O devices. Hence these are known as memory read or I/O read machine cycles. These, machine cycles have 3 T-states., A simple example for memory read machine cycle is MVI D, 24H, For the above example there are 2 machine cycles involved. One is the Opcode fetch cycle and the, second one is the memory read cycle which transfers the operand 24H from the memory to the, microprocessor., T1 state: In this state the contents of the program counter is placed on the higher order address bus, (A8-A15) and lower order address and data multiplexed (AD0-AD7) bus. ALE goes high so that the, memory latches the (AD0-AD7) and then during the middle of the T1 state ALE goes low, so that, complete 16-bit address are available., The microprocessor then identifies the memory read machine cycle from the status signals IO/M’=0,, S1=1, S0=0. This condition indicates the memory read cycle., T2 state: Selected memory location is placed on the (D0-D7) of the A/D multiplexed bus., T3 State: The data which was loaded on the previous state is transferred to the microprocessor. In the, middle of the T3 state RD’ goes high and disables the memory read operation. The data which was, , 27

Page 27 :

obtained from the memory is then decoded., The concept can be understood better with the aid of the diagram shown below., , Fig.1.22 : I/O read machine cycle, This machine cycle is very similar to memory read machine cycle. It is a 2 byte-I/O read instruction., A simple example is IN 22H., The first machine cycle is same as the memory read machine cycle, which is the Opcode fetch cycle., The second machine cycle is the I/O read machine cycle, where the content of port addresses (22H in, this case) is transferred to the microprocessor., The status signal for the I/O read machine cycle is different. The status signal values are IO/M’=1,, S1=1, S0=0., In the next article let us continue with the other 4 types of the machine cycle., , 28

Page 28 :

1.6, MEMORY INTERFACING : Microprocessor need to access memory quite frequently, to readinstructions and data stored in memory; the interface circuit enables that access., , Fig.1.23 Memory Interfacing, The interface process involves designing a circuit that will match the memoryrequirements with the, microprocessor signal.[Memory has certain signalrequirements to read from and write into memory., SimilarlyMicroprocessor initiates the set of signals when it wants to read fromand write into, memory]., , Fig 1.24: Static RAM and EPROM memory, Accessing memory can be summarized into the following three steps:, Select the chip., , 29

Page 29 :

Identify the memory register., Enable the appropriate buffer., And to Translating this to microprocessor domain following steps are required:, The microprocessor places a 16-bit address on the address bus., Part of the address bus will select the chip and the other part will gothrough the address decoder to, select the register., The signals IO/M and RD combined indicate that a memory read operation is in progress. The, MEMR signal can be used to enable theRD line on the memory chip., Address Decoding : The result of ‘address decoding’ is the identification of a register for a given, address. A large part of the address bus is usually connected directly to the address inputs of the, memory chip. This portion is decoded internally within the chip. What concerns us is the other partthat, must be decoded externally to select the chip. This can be done either using logic gates or a decoder., Interfacing circuit :, , Fig 1.25 Interfacing 2732 EPROM with 8085 Microprocessor, The 8085 address lines A11-A0 are connected to the pins A11-A0 of the memory chip.Decoder, decode A15-A12 and output O0 is connected to CE’ which is asserted onlywhen A15-A12 is 0000, (A15 low enables decoder and input 000 asserts the output O0).One control signal MEMR’ is, connected to OE’ to enable output buffer., Example: Interface a 4K EPROM, one 4K RAM and one 8K RAM to a microprocessor withthe, following Memory Map., , 30

Page 30 :

Fig. 1.26 Memory Map, A memory chip select decoder is used to provide chip select signal for eachmemory device (IC). This, will decide the address range that is allotted for each memoryIC. 74LS138 is a 3 to 8 decoder and it can, be used for this purpose. In this example theminimum memory block size is 4K. To access 1K, locations 10 address lines must be used(210 =1K = 1024 locations). So to access 4K locations (4 X, 1K = 22 X 210 = 212) 12address lines (A0 – A11) must be used. Since 8085 has 16 address lines the, decoding can, be indicated as shown below., , Fig 1.27 Variable address lines, , Fig. 1.28: Memory Interface Circuit, , 31

Page 31 :

CHAPTER 2, 2.1 BASIC INTERFACING CONCEPTS, Memory is made up of (registers). Each register consists of one storage location. Each location, consists of an address. The number of storage locations from few hundreds to several mega or giga, locations. The total number of memory storage is calledmemory capacity and measured in Bytes., Each register consists of storage element (FF, capacitor for semiconductor). A storage element is, called cell. The data could be read from or written to memory., 2.1.1 Memory structure and its requirements, Read/write memories consist of an array of registers, in which each register has unique address. The, size of the memory is N x M as shown below where N is the number of registers and M is the word, length, in number of bits., , Fig 2.1 Logic diagram for RAM, If memory is having 12 address lines and 8 data lines, then Number of registers/ memory locations, (capacity) = 2N= 212 = 4096, Word length = M bit = 8 bit, Example 2: If memory has 8192 memory locations, then it has 13 address lines. Table 2.1 shows, how the number of address lines are decided depending on the size of memory., , 32

Page 32 :

Table 2.1 summarizes capacity with address, Memory Capacity, 1k = 1024 memory locations, 2k = 2048 memory locations, 4k = 4096 memory locations, 8k = 8192 memory locations, 16k = 16384 memory locations, 32k = 32768 memory locations, 64k = 65536 memory locations, , Address lines, required, 10, 11, 12, 13, 14, 15, 16, , 2.2 INTERFACING OUTPUT DISPLAYS, The output devices are usually slow. Also the output is usually expected to continue appearing on the, output device for a long period of time. Given that the data will be present on the data lines for a very, short period (microseconds), it has to be latched externally. To do this external latch should be, enabled when the port’s address is present on the address bus, the IO/M signal is high and WR is set, low. The resulting signal would be active when the output device is being accessed by the, microprocessor., 2.3 INTERFACING INPUT DEVICES, The basic concepts are similar to interfacing of output devices. The address lines are decoded to, generate a signal that is active when the particular port is being accessed. An IORD signal is, generated by combining the IO/M and the RD signals from the microprocessor. A tristate buffer is, used to connect the input device to the data bus. The control (enable) for these buffers is connected to, the result of combining the address signal and the signal IORD., 2.4 MEMORY MAPPED I/O, Basic Memory Interfacing with 8085, For interfacing memory devices to µp 8085, following points should be considered:, , , µp 8085 can access 64KB memory since address bus is 16-bit., , , , Generally EPROM (or EPROMs) is used as a program memory and RAM (or RAMs) asdata memory., , , , The capacity of program memory and data memory depends on the application., , , , It is not always necessary to select 1 EPROM and 1 RAM. We can have multiple EPROMs and, multiple RAMs as per the requirement of application., For Example, We have to implement 32 KB of program memory and 4KB EPROMs are available. In this case we can, connect 8 EPROMs in parallel. We can place EPROM/RAM anywhere in full 64 KB address space., But program memory (EPROM) should be located from address 0000 H. It is not always necessary, to locate EPROM and RAM in consecutive memory address. The memory interfacing requires to:, , 33

Page 33 :

Enable the appropriate buffer, , , , Select the chip, Identify the register, , , , , µp system includes memory and I/O devices., It is important to note that µp can communicate (read/write) with only one device at, a time, so address decoding needed., Address Decoding techniques There are two main techniques:, , , , , Absolute decoding/ Full Decoding, Linear decoding / Partial Decoding, Absolute Decoding: All the higher address lines are decoded to select the memory chip, and the, memory chip is selected only for the specified logic level on these high-order address, no other logic, levels can select the chip. The Fig 2.2 shows the memory interface with absolute decoding. This, addressing technique is normally used in large memory systems., , Fig 2.2 Absolute Address Decoding, Linear Decoding- In small systems, h/w for the decoding logic can be eliminated by using, individual high-order address lines to select memory chips. This is referred to as linear decoding., The Fig 2.3 below shows the addressing of RAM with linear decoding technique.This technique is, also called partial decoding. It reduces the cost of the decoding circuit, but it has a drawback of, multiple address (shadow addresses)., , 34

Page 34 :

Fig 2.3 Linear Decoding, Interfacing Examples:, Draw the circuit diagram of an 8085 system, having a 4 KB EPROM and two 8 KB RAM ICs. The, starting address of the EPROM is 0000H and that of RAM is 8000H. The address of the decoder, circuits should be clearly shown., Answer :, EPROM-4 KB (Address lines required is 12 – A0 to A11)RAM-I-8 KB (Address lines required is 13 –, A0 to A12)RAM-II-8 KB (Address lines required is 13 – A0 to A12), Mapping of Addresses to Memory Ics, Table 2.2 Address Mapping, , 35

Page 35 :

Fig 2.4 Address Decoding, 2.5 Flow chart symbols, To develop the programming logic, programmer has to write down various actions which are to be, performed in proper sequence. The flow chart is a graphical tool that allows programmer to, represent various actions which are to be performed. Figure 2.5 shows the graphical symbols used in, flow chart, Fig 2.5 Graphical symbols used in flow chart, 1. Oval: indicates start or stop operation., , 2. Arrow: indicates flow with direction, 3. Parallelogram: indicates input/output operation., 4. Rectangle: indicates process operation, 5. Diamond: indicates decision making operation, , 38

Page 36 :

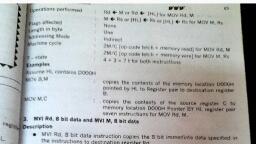

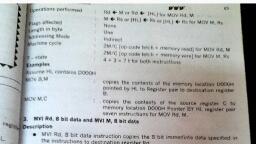

6. ouble sided rectangle: indicates execution of3s7ubroutine, 7. Circle with alphabet: indicates continuation., 2.6 DATA TRANSFER INSTRUCTIONS, Opcode, source to destination, MOV Rd, Rs M, Rs Rd, M, , Move immediate 8-bit, MVI Rd, data M, data, , Load accumulator, LDA 16-bit address, , Load accumulator indirect, LDAX B/D Reg.pair, , Store accumulator direct, STA 16-bit address, , Store accumulator indirect, , Operand, , DescriptionCopy from, , This instruction copies the contents of the source, register into the destination register; the contents of, the source register are not altered. If one of the, operands is a memory location, its location is specified, by the contents of the HL registers., Example: MOV B, C or MOV B, M, The 8-bit data is stored in the destination register or, memory. If the operand is a memory location, its, location is specified by the contents of the HL, registers., Example: MVI B, 57 or MVI M, 57, , The contents of a memory location, specified by a16bit address in the operand, are copied to the, accumulator. The contents of the source are not altered., Example: LDA 2034 or LDA XYZ, , The contents of the designated register pair point to a, memory location. This instruction copies the contents, of that memory location into the accumulator. The, contents of either the register pair or the memory, location are not altered., Example: LDAX B, The contents of the accumulator are copied into the, memory location specified by the operand. This is, a 3-byte instruction, the second byte specifies the loworder address and the third byte specifies the highorder address., Example: STA 4350 or STA XYZ, , Reg. pair The contents of the accumulator are copied into the memory location specified by the contents of, the operand (register pair). The contents of the accumulator are not altered., Example: STAX B, , 39

Page 37 :

Load register pair immediate, LXI Reg. pair, 16-bit data The instruction loads 16-bit data in the register pair designated in the, operand.Example: LXI H, 2034, Load H and L registers direct, The instruction copies the contents of the memory location pointed out by the 16-bit address into, register L and copies the contents of the next memory location into, register H. The contents of source memory locations arenot altered., Example: LHLD 2040, Store H and L registers direct, The contents of register L are stored into the memory location specified by the 16-bit address in, the operand and the contents of H register are stored into the next memory location by incrementing, the operand. The contents of registers HL are not altered. This is a 3-byte instruction, the second byte, specifies the low-order address and the third byte specifies the high-order address., Example: SHLD 2470, Exchange H and L with D and E XCHG none, The contents of register H are exchanged with the contentsof register D, and the contents of register L, are exchanged with the contents of register E., Example: XCHG, 2.7 ARITHMETIC INSTRUCTIONS, Opcode, ADD, , Operand, DescriptionAdd register or memory to accumulator, R, The contents of the operand (register or memory) arM, the contents of the accumulator and the result is stored in the accumulator. If the, operand is a memory location, its location is specified by the contents of the HLregisters. All flags are, modified to reflect the result of the addition., Example: ADD B or ADD M, Add register to accumulator with carry, ADC, R, The contents of the operand (register or memory), and the, M, Carry flag are added to the contents of the accumulator and the result is, stored in the accumulator. If the operand is a memory location, its, location is specified by the contents of the HL registers. All flags are, modified to reflect the result of theaddition., Example: ADC B or ADC M, , Add immediate to accumulator, , 40

Page 38 :

ADI 8-bit data, The 8-bit data (operand) is added to the contents of the, accumulator and the result is stored in the accumulator. All flagsare modified to reflect the result of the, addition., Example: ADI 45, Add immediate to accumulator with carry, The 8-bit data (operand) and the Carry flag are added to thecontents of the accumulator and the result, is stored in the accumulator. All flags are modified to reflect the result of the addition., Example: ACI 45, Add register pair to H and L registers, The 16-bit contents of the specified register pair are added to the contents of the HL register and the, sum is stored in the HL register. The contents of the source register pair arenot altered. If the result is, larger than 16 bits, the CY flag isset. No other flags are affected., Example: DAD H, The contents of the operand (register or memory ) are subtracted from the, SUB R contents of the accumulator, and the result is stored in the accumulator. If, M the operand is a memory location, its location is specified by the contents, of the HL registers. All flags are modified to reflect the result of the, subtraction., Example: SUB B or SUB M, Subtract source and borrow from accumulator, SBB, R The contents of the operand (register or memory ) and the, Borrow flag are subtracted from the contents of the accumulator and the result is placed in the, accumulator. If the operand is a memory location, its location is specified by the contents of the HL, registers. All flags are modified to reflect the result in accumulator., Example: SBB B or SBB M, Subtract immediate from accumulator, The 8-bit data (operand) is subtracted from the contents of the accumulator and the result is stored in, the accumulator. All flags are modified to reflect the result of the subtraction., Example: SUI 45, Subtract immediate from accumulator with borrow, The 8-bit data (operand) and the Borrow flag are subtracted from the contents of the accumulator, and the result is stored in the accumulator. All flags are modified to reflect the result of the, subtracion., Example: SBI 45, , 41

Page 39 :

Increment register or memory by 1INR R, M, Increment register pair by 1, The contents of the designated register or memory) are incremented by 1 and the result is stored in, the same place. If the operand is a memory location, its location is specified by the contents of the HL, registers., Example: INR B or INR M, The contents of the designated register pair are incremented by1 and the result is stored in the same, place., Example: INX H, Decrement register or memory by 1, DCR R, M, , The contents of the designated register or memory are, decremented by 1 and the result is stored in the same place. If the, operand is a memory location, its location is specified by the, contents of the HL registers., Example: DCR B or DCR M, , Decrement register pair by 1, , 42

Page 40 :

The contents of the designated register pair are decremented by 1 and the result is stored in the, same place. Example: DCX H, Decimal adjust accumulator, The contents of the accumulator are changed from a binary value to two 4-bit binary coded decimal, (BCD) digits. This is the only instruction that uses the auxiliary flag to perform the binary to BCD, conversion, and the conversion procedure is described below. S, Z, AC, P, CY flags are altered to, reflect the results of the operation., If the value of the low-order 4-bits in the accumulator is greater than 9 or if AC flag is set, the, instruction adds 6 to thelow-order four bits., If the value of the high-order 4-bits in the accumulator is greater than 9 or if the Carry flag is set, the, instruction adds 6to the high-order four bits., Example: DAA, 2.8 LOGICALINSTRUCTIONS, Opcode, , Operand, , DescriptionCompare register or memory with, , accumulator, CMP, R, The contents of the operand (register or, memory) are, compared with the contents of the accumulator. Bothcontents are preserved . The result of the, comparison is shown by setting the flags of the PSW as follows:if (A) < (reg/mem): carry flag is set,, s=1, if (A) = (reg/mem): zero flag is set, s=0, if (A) > (reg/mem): carry and zero flags are reset, s=0 Example: CMP B or CMP M, Compare immediate with accumulator, The second byte (8- bit data) is compared with the contents of the accumulator. The values being, compared remain unchanged. The result of the comparison is shown by setting the flags of the PSW, as follows:, if (A) < data: carry flag is set, s=1if (A) = data: zero flag is set, s=0, if (A) > data: carry and zero flags are reset, s=0 Example: CPI 89, Logical AND register or memory with accumulator, ANA, , RM, , The contents of the accumulator are logically ANDed with the contents, of the operand (register or memory), and the result is placed in the, accumulator. If the operand is a memory location, its address is, specified by the contents of HL registers. S, Z, P are modified to reflect, the result of the operation. CY is reset. AC is set., Example: ANA B or ANA M, , Logical AND immediate with accumulator, The contents of the accumulator are logically, ANI, 8-bit data, ANDed with, the 8-bit data (operand) and the result is placed in the accumulator. S, Z, P are modified to reflect the, , are affected4.3Example: CMA

Page 41 :

result of theoperation. CY is reset. AC is set., Example: ANI 86, Exclusive OR register or memory with accumulator, XRA, RM, The contents of the accumulator are Exclusive ORed with the contents, of the operand (register or memory), and the result is placed in the, accumulator. If the operand is a memory location, its address is, specified by the contents of HL registers. S, Z, P are modified to, reflect the result of the operation. CY and AC are reset., Example: XRA B or XRA M, Logical OR register or memory with accumulator, , are affected4.3Example: CMA

Page 42 :

ORA, , 45, , RM

Page 43 :

The contents of the accumulator are logically ORed with the contents of the operand, (register/memory), and the Result is placed in the accumulator. If the operand is a memory location,, its address is specified by the contents of HL registers. S, Z, P are modified to reflect the result of the, operation. CY and AC are reset., Example: ORA B or ORA M, Exclusive OR immediate with accumulator, The contents of the accumulator are Exclusive ORed with the 8-bit data (operand) and the result is, placed in the accumulator. S, Z, P are modified to reflect the result of the operation. CY and AC are, reset., Example: XRI 86, Logical OR immediate with accumulator, The contents of the accumulator are logically ORed with the 8-bit data (operand) and the result is, placed in the accumulator. S, Z, P are modified to reflect the result of the operation. CY and AC are, reset., Example: ORI 86, Complement accumulator, CMA none, No flags, , The contents of the accumulator are complemented., , Complement carry, CMC none, affected., , The Carry flag is complemented. No other flags are, Example: CMC, , Set Carry, STC none, , The Carry flag is set to 1. No other flags are affected., Example: STC, , 2.9 BRANCHING INSTRUCTIONS, Opcode, Operand, DescriptionJump unconditionally, JMP, 16-bit address, The program sequence is transferred to the memory, location, specified by the 16-bit address given in the operand.Example: JMP 2034 or JMP XYZ, Jump conditionally, Operand: 16-bit address, The program sequence is transferred to the memory location specified by the 16- bit address given in, the operand based onthe specified flag of the PSW as described below., Example: JZ 2034 or JZ XYZ, Opcode, JC, JNC, JP, JM, JZ, , Description, Jump on Carry, Jump on no Carry, Jump on positive, Jump on minus, Jump on zero, , Flag Status, CY = 1, CY = 0, S=0, S=1, Z=1, , 46

Page 44 :

JNZ, JPE, JPO, , Jump on no zero, Jump on parity even, Jump on parity odd, , Z=0, P=1, P=0, , Unconditional subroutine call, CALL, 16-bit address, The program sequence is transferred to the memory, location, specified by the 16-bit address given in the operand. Before the transfer, the address of the next, instruction after CALL (the contents of the program counter) is pushed onto the stack.Example:, CALL 2034 or CALL XYZ, Call conditionally Operand: 16-bit address, The program sequence is transferred to the memory location specified by the 16-bit address given in, the operand based on the specified flag of the PSW as described below. Before the transfer, the, address of the next instruction after the call (the contents of the program counter) is pushed onto the, stack., Example: CZ 2034 or CZ XYZ, , Opcode Description, Call on Carry, CNC Call on no Carry, CP, Call on positive, CM, Call on minus, CZ, Call on zero, CNZ Call on no zero, CPE Call on parity even, CPO Call on parity odd, , Flag Status, CY = 1, CY = 0, S=0, S=1, Z=1, Z=0, P=1, P=0, , CC, , Return from subroutine unconditionally, The program sequence is transferred from the subroutine to the calling program. The two bytes, from the top of the stack are copied into the program counter, and program execution begins at the, new address., Example: RET, Return from subroutine conditionally, Operand: none, The program sequence is transferred from the subroutine to the calling program based on the, specified flag of the PSW as described below. The two bytes from the top of the stack are copied into, the program counter, and program execution begins at the new address., Example: RZ, , 47

Page 45 :

Opcode, RC, RNC, RP, RM, RZ, RNZ, RPE, RPO, , Description, Return on Carry, Return on no Carry, Return on positive, Return on minus, Return on zero, Return on no zero, Return on parity even, Return on parity odd, , Flag Status, CY = 1, CY = 0, S=0, S=1, Z=1, Z=0, P=1, P=0, , Load program counter with HL contents, The contents of registers H and L are copied into the program counter. The contents of H are placed, as the high-order byte and the contents of L as the low-order byte., Example: PCHL, Restart, The RST instruction is equivalent to a 1-byte call instruction to one of eight memory locations, depending upon the number. The instructions are generally used in conjunction with interrupts and, inserted using external hardware. However these can be used as software instructions in a, program to transfer program execution to one of the eight locations. Theaddresses are:, Instruction, RST 0, RST 1, RST 2, RST 3, RST 4, RST 5, RST 6, RST 7, , Restart Address, 0000H, 0008H, 0010H, 0018H, 0020H, 0028H, 0030H, 0038H, , The 8085 has four additional interrupts and these interrupts generate RST instructions internally and, thus do not require any external hardware. These instructions and their Restart addresses are:, Interrupt, , Restart Address, , TRAP, RST 5.5, RST 6.5, RST 7.5, , 0024H, 002CH, 0034H, 003CH, , 2.10 WRITING ASSEMBLY LANGUAGE PROGRAMMS, 1., Store the data byte 32H into memory location 4000H. MVI A, 52H : Store 32H inthe, accumulator, STA 4000H :, HLT :, , Copy accumulator contents at address 4000H, Terminate program execution, , 48

Page 46 :

Program 2:, LXI H :, MVI M :, register pair, HLT :, 2., , Load HL with 4000H, Store 32H in memory location pointed by HL, Terminate program execution, Exchange the contents of memory locations 2000H and 4000H.Program 1:, , LDA 2000H, : Get the contents of memory location 2000H into accumulatorMOV, B, A, : Save the contents into B register, LDA 4000H, : Get the contents of memory location 4000Hinto accumulatorSTA, Get the contents of mem4o6ry location 4000H into A register, LDAX D 2000H, : Store the contents of accumulator at address 2000H, MOV A, B, : Get the saved contents back into A register, STA 4000H : Store the contents of accumulator at address 4000HProgram 2:, LXI H 2000H, LXI D 4000H, MOV B, M, MOV M, A, A, B, STAX D, , : Initialize HL register pair as a pointer to memory location 2000H., : Initialize DE register pair as a pointer to memory location 4000H., : Get the contents of memory location 2000H into B register., : Store the contents of A register into memory location 2000H.MOV, : Copy the contents of B register into accumulator., : Store the contents of A register into memory location 4000H. HLT, : Terminate program execution., , 3., Find the 2's complement of the number stored at memory location 4200H and store the, complemented number at memory location 4300H., Source program:, LDA 4200H, CMA, ADI, 01 H, STA 4300H, HLT, , : Get the number, : Complement the number, : Add one in the number, : Store the result, : Terminate program executionFlow chart:, Fig 2.6 Flow Chart, , 49

Page 50 :

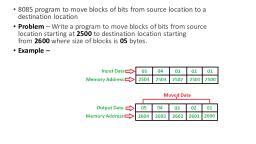

Fig 2.10 Flow Chart, Source program:, LDA 4200H : Get the packed BCD number ANI FOH : Mask lower nibble, RRCRRCRRC, RRC : Adjust higher BCD digit as a lower digitSTA 4301H : Store the partial result, LDA 4200H : .Get the original BCD number ANI OFH : Mask higher nibble, STA 4201H : Store the result, HLT : Terminate program execution, ADDRESSING MODES, Every instruction of a program has to operate on a data. The method of specifying the data to be, operated by the instruction is called Addressing., The 8085 has the following 5 different types of addressing., , 53

Page 51 :

1. Immediate Addressing, 2. Direct Addressing,, 3. Register Addressing, 4. Register Indirect Addressing, 5. Implied Addressing, Immediate Addressing, In immediate addressing mode, the data is specified in the instruction itself. The data will be apart of, the program instruction. All instructions that have ‘I’ in their mnemonics are of Immediate, addressing type., Eg.MVI B, 3EH- Move the data 3EH given in the instruction to B register., Direct Addressing, In direct addressing mode, the address of the data is specified in the instruction. The data will be in, memory. In this addressing mode, the program instructions and data can be stored in, differentmemory blocks. This type of addressing can be identified by 16bit address present in theinstruction., Eg.LDA 1050H- Load the data available in memory location 1050H in accumulator., Register Addressing, In register addressing mode, the instruction specifies the name of the register in which the data is, available. This type of addressing can be identified by register names (such as ‘A’, ‘B’ .................... ) in the, instruction., Eg. MOV A, B -Move the content of B register to A register., Register Indirect Addressing, In register indirect addressing mode, the instruction specifies the name of the register in which the, address of the data is available. Here the data will be in memory and the address will be in the, register pair. This type of addressing can be identified by letter ‘M’ present in the instruction., Eg. MOV A, M - The memory data addressed by HL pair is moved to A register., Implied Addressing, In implied addressing mode, the instruction itself specifies the type of operation and location of data, to be operated. This type of instruction does not have any address, register name, immediate data, specified along with it. Eg. CMA - Complement the content of accumulator, 2.11 PROGRAMMING TECHNIQUES, Looping-In this technique, the program is instructed to execute certain set of instructions repeatedly, toexecute a particular task number of times., Counting-This technique allows programmer to count how many times the instruction/set of, instructionsare executed., Indexing-This technique allows programmer to point or refer the data stored in sequential, memorylocation one by one., , 54

Page 52 :

CHAPTER 3, 3.1 ADDITIONAL DATA TRANSFER AND 16 BIT ARITHMETIC INSTRUCTION, The data transfer operations are:, 1.MVI rd , byte :- This instruction moves the immediate data givenafter the instruction into register rd., 2.MOV rd , rs :- This instruction moves data from register rs toregister rd., 3. LXI rp, 16-bit:- This instruction moves 16-bit data or address toregister pair., 4., XCHG: The contents of register H are exchanged with the contents of register D, and the, contents ofregister L are exchanged with thecontents of register E., 3.2 ARITHMETIC OPERATIONS RELATED TO MEMORY, Examples:, 1., Calculate the sum of series of numbers. The length of series is in memory location, 2200H and seriesitself begins from 2201H., (a) Assume the sum to be 8 bit number, so ignore carry. Store the sum at 2300H., (b), Assume the sum to be 16 bit number. Store the sum at memory locations 2300H &, 2301H.(a), LDA 2200HMOV C,A SUB A, LXI H, 2201H, BACK: ADD M INX H DCR C, JNZ BACKSTA 2300HHLT, (b), LDA 2200H MOV C,A LXI H,2201HSUB A, MOV B, A, Y: ADD M JNC XINR B INX HDCR CJNZ Y, STA 2300HMOV A, B STA 2301HHLT, 2., Multiply two 8-bit numbers stored in memory location 2200H & 2201H. Store the, result in memorylocation 2300H & 2301H., , LDA 2200H, , 53

Page 54 :

Rotate accumulator left through carry, , 57

Page 56 :

Each binary bit of the accumulator is rotated right by one position. Bit D0 is placed in the position of, D7 as well as in the Carry flag. CY is modified according to bit D0. S, Z, P,AC are not affected., Example: RRC, Each binary bit of the accumulator is rotated left by one position through the Carry flag. Bit D7 is, placed in the Carryflag, and the Carry flag is placed in the least significant position D0. CY is, modified according to bit D7. S, Z, P, ACare not affected. Example:RAL, Rotate accumulator right through carry, Each binary bit of the accumulator is rotated right by one position through the Carry flag. Bit D0 is, placed in the Carryflag, and the Carry flag is placed in the most significant position D7. CY is, modified according to bit D0. S, Z, P, ACare not affected. Example:RAR, Compare register or memory with accumulator, CMP, R, The contents of the operand (register or memory) are, compared with the contents of the accumulator. Bothcontents are preserved . The result of the, comparison is shown by setting the flags of the PSW as follows:, if (A) < (reg/mem): carry flag is set, s=1 if (A), = (reg/mem): zero flag is set, s=0, if (A) > (reg/mem): carry and zero flags are reset, s=0Example: CMP B or CMP M, Compare immediate with accumulator, The second byte (8- bit data) is compared with the contents of the accumulator. The values being, compared remain unchanged. The result of the comparison is shown by setting the flags of the PSW, asfollows:, if (A) < data: carry flag is set, s=1 if (A), = data: zero flag is set, s=0, if (A) > data: carry and zero flags are reset, s=0Example: CPI 89, 3.4 COUNTER AND TIME DELAYS, A loop counter is set up by loading a register with certain value. Then using DCR and INR the contents, of register are modified. A loop is set up with a conditional jump that looks back or not depending on, whether the count has reached the termination count. The operation of a counter can be described using, flow chart as shown in Figure 3.4, , 69

Page 57 :

Fig 3.3Flow Chart, Implementing loop using DCR instruction:MVI C, 15H, LOOP:DCR C, JNZ LOOP, Using a register pair as a loop counter:, Using a single register, one can repeat a loop for maximum 255 times., LXI B, 100HLOOP: DCX B, MOV A, CORA B JNZ LOOP, Delay Routine, Delay routines are subroutines used for maintaining the timings of various operations inmicroprocessor.In, control applications, certain equipment needs to be ON/OFF after a specified time delay. In some, applications, a certain operation has to be repeated after a specified time interval. In such cases,, simple time delay routines can be used to maintain the timings of the operations., DELAY ROUTINE PROCESS, A delay routine is generally written as a subroutine (It need not be a subroutine always. It can, beeven a part of main program). In delay routine a count (number) is loaded in a register of, microprocessor. Then it is decremented by one and the zero flag is checked to verify whether, thecontent of register is zero or not. This process is continued until the content of register is, zero.When it is zero, the time delay is over and the control is transferred to main program to carry out, the desired operation., The delay time is given by the total time taken to execute the delay routine. It can be computed by, multiplying the total number of T-states required to execute subroutine and the time for one T-state of, the processor. The total number of T-states can be computed from the knowledge of T-states required, for each instruction. The time for one T-state of the processor is given by the inverse of the internal, clock frequency of the processor., For example, if the 8085 microprocessor has 5 MHz quartz crystal then, the internal clock frequency =, 5 /2 = 2.5 MHz, Time for one T-state= 1 / 2.5 x 106= 0.4µsec, • For small time delays (< 0.5 msec) an 8- bit register can be used., • For large time delays (< 0.5 Sec) l6-bit register should be used., •, For very large time delays (> 0.5 sec), a delay routine can be repeatedly, called in themain program., The disadvantage in delay routines is that the processor time is wasted. An alternate solution is to, usededicated timer like 8253/8254 to produce time delays or to maintain timings of various, operations., EXAMPLE DELAY ROUTINE, 1., Write a delay routine to produce a time delay of 0.5 msec in 8085 processor-based, system whose clocksource is 6 MHz quartz crystal., Solution, , 70

Page 58 :

The delay required is 0.5 msec, hence an 8-bit register of8085 can be used to store a Count value and, thendecrement to zero. The delay routine is written as a subroutine as shown below., Delay routine, Loop: DCR D, JNZ Loop, RET, , ; Decrement the count., ; If count is zero go to, ; Return to main program., , The following table shows the T-state required for execution of the instructions in the subroutine., Table 3.1 Calculation to find the count value, Instruction, T-State requiredfor, Number of times, execution of, theinstruction is, aninstruction, executed, CALL addr16, 18, 1, MVI D, N, 7, 1, DCR D, 4, N times, JNZ LOOP, 10, (N-1) times, 7, 1, RET, 10, 1, TOTAL T-STATES FOR DELAY SUBROUTINE, , Total T-States, , 18 x 1 = 18, 7x1=7, 4 x N = 4N, 10 x (N-1) = 10N – 10, 7x1=7, 10 x 1 = 10, 14N + 32, , Calculation to find the count value, N:, External clock frequency = 6 Mhz, Internal clock frequency = External Frequency / 2= 6 / 2= 3 Mhz, Time period for 1 T-State= 1 / Internal clock frequency= 1 / 3x106= 0.333µS, No. of T-states requiredfor delay of 0.5mS = Required time delay / Time for one T-state, = 0.5mS / 0.333µS= 1500.10≈ 1500 = 150010, From above table, we know that;14N + 32 = 1500, N = (1500 – 32) / 14 = 104.85710≈ 10510= 69H, Therefore by replacing the count value, N by 69H in the above program , a delay of 0.5mSec can, beproduced, 2., Write an ALP for 8085 to count from AAHto 00H, with a time delay of 2ms for each, count. Assumethe external frequency given to the processor is 2MHz., Internal Frequency in 8085 = External frequency / 2ie.,= 2Mhz / 2= 1Mhz1, T-State= 1 / f (internal frequency)= 1µS, Main program for counting from AA to 00, MVI C, AAH, Loop:CALL Delay, DCR C, JNZ LoopHLT, Delay program for delay of 2ms, , 71

Page 60 :