Page 1 :

introduction, , Flip-flop is a 1 bit me, increase the storage capaci, Rep. Such a group of flip-fl, , Mory cell w!, ty in terms, , — ‘Ops is known as a register., shift eB, , 3, a», , hich can be used for storing the digital data. To, of number of bits, we have to use a group of flip, f rg tal va ae a shift fegister is a cascade of flip flops, sharing the same clock, in, which the output of each flip-flop is connected to the ‘data’ input of the next flip-flop in, the chain, |resulting in a circuit that shifts by one position the ‘bit array’ stored in it,, shifting in the data Present at its input and ‘shifting out' the last bit in the array, at each, transition of the clock input., , the Shift Register is another type of sequential logic circuit that can be used for the, storage or the transfer of data in t, , ¢ he form of binary numbers.{This sequential device loads, the data present on its inputs and then moves or “shifts” it to its output once every clock, cycle, hence the name “shift register”., , ars, , Ld, , More generally, a shift register may be multidimensional, such that its ‘data in' and, stage outputs are themselves bit arrays: this is implemented simply by running several, shift registers of the same bit-length in parallel., , A shift register basically consists of several single bit “D-Type Data Latches”, one for, each data bit, either a logic “0” or a “1”, connected together in a serial type daisy-chain, arrangement so that the output from one data latch becomes the input of the next latch, and so on, ee ‘, , The number of individual data latches required to make up a single Shift Register, device is usually determined by the number with the most common, being 8-bits wide constructed from eigh, , so that they, one of four

Page 2 :

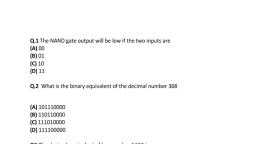

a'n° . Digital Electronic (F.Y.B.Sc. IT.) (Sem,, Serial-in to Serial-out (SISO) : The data is shifted serially “IN” and “OUT” of the, Tegister, one bit at a time in either a left or right direction under clock control., Parallel-in to Serial-out (PISO) : The parallel data is loaded into the registo,, simultaneously and is shifted out of the register serially one bit at a time unde,, clock control. :, , © Parallel-in to Parallel-out (PIPO) : The parallel data is loaded simultaneously into, the register, and transferred together to their respective outputs by the same clock —, , , , , , , , , , , , , , , , , , , , , , pulse., The effect of data movement from left to right through a shift register can be, presented graphically as :, Parallel Data Output, Q Q Q Q, [use { { {isp, T T T T, . Q Serial, pawl 2s Sees ee res Data, cok Output, Input 1~bit 1~bit 1—bit 1-bit ss, MSB | | hiss, D, D, D, D,, _—_—_—_—_—_—_—_—__, Parallel Data Input, , Also, the directional movement of the data through a shift register can be either to the, left, to the right, left-in but right-out, or both left and right shifting within the same, register thereby making it bidirectional., , Applications of shift register ", , A shift register is a digital memory circuit found in calculators, computers, and dataprocessing systems. Bits enter the shift register at one end and emerge from the other end., The two ends are called left and right. Flip flops, also known as bistable gates, store and, process the data. In its most basic form, i ister is a bidirectional FIFO (first-in, , , , , , , , , , , , , , , , , , , , , first-out) circuit. When a bit is inpu ie in the register move one place, to the right, and the rightmost bit disappear: on the right, all the bits, move one place to the left, and the le Tegisters are commonly, used in converters that translate, , , , or vice-versa. Shift registers

Page 3 :

ither to the, , , , a. left or shifted we, aa: 10, eaves Out hn One bit ata ce Tight. Since there is only one output, the DATA — PH, , egister or Ss], As the data is feg Sa., , : from right as hj, it SISO shift register eanaiis ri by bit the shift register shifts the data bits to left. A, , sgister is one of the simp! 'p flops and only th ions. The SISO shift, . st ly three connections. The sl, she serial input (SI) hich a, pee the four configurations as it has only three connections,, 0) which is taken from the ue what enters the left hand flip-flop, the serial output, signal (Clik). The logic circuit dia “a of the right hand flip-flop and the sequencing clock, Sram below shows 4 bit serial-in serial-out shift register., , me ‘in a serial! pattern, hence the name Serial-in to, , , , , , oF 10 0, 0 1, DESO Q, FFD Serial, Data out, CLK, , , , , , , , , , , , , , The registers which will shift the bits to left are called “Shift left registers”. The, registers which will shift the bits to right are called “Shift right registers”. ig, , This type of Shift Register also acts as a temporary storage device or it can act as a, time delay device for the data, with the amount of time delay being controlled by the, number of stages in the register, 4, 8, 16 etc. or by varying the application of the clock, pulses., Serial in Parallel Out, , 4-bit Parallel Data Output, ee Q,!

Page 4 :

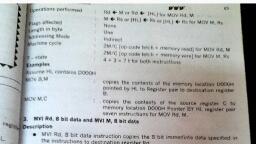

=e, , S's Digital Electronic (F-Y-B.Sc. LT.) (Sem.-1, , the Fi . effect of each Clock Pulse is to shift the data contents of each stage one Place’ tg:, ht, and this is shown in the ‘following table until the complete data value o¢, , of see in the register. This data value can now be read directly from the outputs., , In such types of Operations, the data is entered serially and taken out in paralle, fashion. Data is loaded bit by bit. The outputs are disabled as long as the data is loading |, As soon as the data loading gets completed, all the flip-flops contain their required data,, the outputs are enabled so that all the loaded data is made available over all the output, , es at the same time. 4 clock cycles are required to load a four bit word. Hence the speeq, of operation of SIPO mode is same as that of SISO mode., Parallel in serial out, , The Parallel-in to Serial-out shift register acts in the opposite way to the serial-in, parallel-out one above. The data is loaded into the register in a parallel format in which, the data bits enter their inputs simultaneously, to the parallel input pins P, to Pp of, , register. The data is then read out sequentially in the normal shift-right mode from |, register at Q representing the data present at Py to Pp., , This data is outputted one bit at a time on each clock cycle in a serial format. It, important to note that with this type of data register a clock pulse is not required, , parallel load the register as it is already present, but four clock pulses are required, unload the data., , a\, , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , efor) D Q Mux)4D @ | fax) DQ) —]mux}} D co) eae Se 4, FA. |* | FEB FFC FED ia, CLK CLK cLK Chee, ss, eee yl a, | Py P. P, Pp, |, 4-it Parallel Data input is, : 4, As this type of shift register converts parallel data, such as an 8-bit data word into, serial format, it can be used ola ¢ t input lines into a single serial, DATA stream which can be se ly |

Page 5 :

: 2 | 0, Fg, SB Parallel ita Output te, Qe tab Oy Oke. ct, Dyed, , FED, , CLK, ial.j = P. P. 1, i, , ‘ - 8, hich all ‘The PIPO shift register j site Parallel Data Input, i ik ;, he the J jonnections, the parallel input (PI) a of the four configurations as it has only three ~, ™ the catput (PO) o the Sequencing clock agra (Ch. what enters the flip-flop, the parallel, , Similar Serial-in to Seri +e, at. Tt ig rary storage device or eas S shift register, this type of register also acts as a, * ried by the frequency eh e delay device, with the amount of time delay being, tired interconnections between th . lock pulses. Also, in this type of register there are no, 4 a e individual flip-flops since no serial shifting of the data is, , required., , , , , , , , , , , , , , , , , , , , , >-Q Ring counter, Serial counter is a uenti Sena ‘ a . 3, RE Sechtecnndghicnicspe | ne, Ring counters are of two types :, j. Ordinary Ring counters., *2. Johnson counter., 4bit Ring Counter, : connection of flip flops, in which the output of ‘last flip, if the output of any stage is 1,, same output throughout the circuit., 7d into means i t of the o then this is transferred to its next, e serial J 2nd oe oy annie the output to its next stage, the output of first flip ‘, over 2 a 0. And this process contin , for all th ae., 7 MES ie