Page 1 :

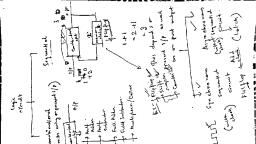

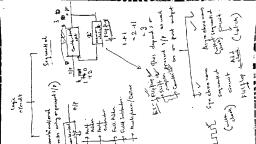

Sequential Circuits, , , , , , , , , , 71, , 7.1.1, , , , Introduction, , The digital circuits discussed in previous chapters were all combinational circuits., In these circuits the input at any particular instant of time solely determines the, output at that instant of time. The sequential circuits are circuits whose output depends, on the present input as well as on past outputs. Thus, sequential circuits contain at, least one memory element which can store binary information in it., , A block diagram of a sequential circuit is shown in figure 7.1., , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , Ir | its ——> t+———> Output: |, np Combinational utpuls ., ; Circuit , Memory, elements, FIGURE 7.1, , Thus, Sequential circuits work in sequence by taking into account the past outputs, as well as the present inputs., , Characteristics of Seqv.enual Circuit, , Characterististics of Sequential Circuits are :, , 1. It is a circuit whose output depends on the present inputs as well as on pas", outputs., , Contain at least one memory element., Difficult to design due to presence of memory., Comparatively slower in speed., , Requires less hardward for its realization., Cheaper in cost., , PnP on, , Scanned with CamScanner

Page 2 :

7.1.2 Difference between Combinational and Sequential Circuit, , Table 7.1 explain the difference between combinational circuit and sequential circuit., TABLE 7.1, , Combinational Circuit, , Sequential Circuit, , , , , , It is a circuit whose outputs at, any time depends only on the, inputs applied to it at that instant, of time., , Contains no memory elements., , Easy to design, due to absence, of memory., , Faster in speed., , Requires more hardware for its, realization., , , , It is a circuit whose output, depends on the present inputs, as well as on past outputs., , Contain at least one memory, element., , Difficult to design due to, presence of memory., , Comparatively slower in speed., , Requires less hardward for its, realization., , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , , | 6. Expensive in cost. Cheaper in cost., 7.2 Clock, A pulse generator within a digital system to which all operations are, synchronized is called clock. Zs, A square wave shown in figure 7.2 is a typical clock waveform used in a digital, system., If, I, |, l, FIGURE 7.2, , Square wave signal has positive clock pulse as well as negative clock pulse., Fig. 7.3(a) shows a positive clock pulse and figure 7.3(b) shows a negative clock, pulse. wt, , [ 160], , , , Scanned with CamScanner

Page 3 :

Leading edge Trailing edge |, , : L, |, Falling’ —.| «— Rising /, , , , , , , , , , , , Rising /—> 1+— Falling/ negative poste, positive negative edge edge, edge edge |, oO, x % | |, 0 Leading edge Trailing edge, , , , , , , , , , , , , , , , , , , , FIGURE 7.3 (A) POSITIVE CLOCK PULSE FIGURE 7.3 (B) NEGATIVE CLOCK PULSE, , In a positive clock pulse, initially, it is at logic level 0 and makes a transition from, logic level 0 to logic level 1 momentarily and then returns to logic level 0. The leading, edge of the pulse is logic level 0 to logic level 1 or positive transition and the trailing, edge is from logic level 1 to logice level 0 or negative transition., , In negative clock pulse, initially, it is at logic level 1. It makes a momentary transition, to logic level 0 followed by a positive transition back to logic level 1., , Hence a square wave signal shown in figure 7.2 could simply be a series of positive, (or negative) clock pulses but the main requirement is that the clock should be, , perfectly periodic., , Flip-Flops, , A flip-flop is a basic memory element used to store one bit of information., Flip flop has two stable states. One of the stable states is known as SET or 1,, whereas the other stable state is called RESET, CLEAR, or u. Normally, there are, , two input lines, (known as data inputs) and two output lines (Q and @). In addition, , to the two data input lines, the FLIP-FLOP has a clock (CLK) line. A train of pulses, is applied at this clock line..The state of the output at any instant of time depends, upon the past outputs and the data inputs present at that instant of time. The state, , can change only when the clock pulse is applied,’, We have many types of flip-flops but all have the following common characteristics., , 1. The output Q and Q are always complementary to each other i.e. if Q=1, then, Q=0 and if Q=0, then Q=1., The circuit has two stable states. i.e. set or 1 and reset or 0., , If the circuit is in set(1) state, it continues to remain in this state and similarly if, it is in Reset(0) state, it continues to remain in this state until the external, signal is changed to change this state., , 5 [ 161}, , Scanned with CamScanner

Page 4 :

7.4 Operating characteristics of Flip-Flop (Latch), One of the simplest ways to understand the operation of a flip-flop is by connecting, two inverters. The output of one inverter is connected to the input of the second, inverter and the output of the second inverter is fed to the input of the first inverter as, shown in figure 7.4., , | A => Q |, , , , , , , , , , , , , , FIGURE 7.4 (LATCH), This circuit has two states either 0 or 1. Let us explain both the states., 1. Set State, Assume that the output of G,=1 i.e. Q=1, which is also the input of G, (B=1)., , Therefore, the output of G, will be 0. i.e. Q=0, which makes A =O and, consequently Q=1 as shown in fig. 7.5., , , , , , , , , , , , , , FIGURE 7.5, , Itis clear from the figure 7.5, that if the circuit (Latch) is in set state, it continues, to remain in this state., , 2. Reset State, , In a similar manner, it can be demonstrated that if Q = 0, then Q=1 and this is, also consistent with the circuit connections as shown in fig. 7.7., , , , , , , , , , FIGURE 7.7, , , , [ 162], , Scanned with CamScanner

Page 5 :

In the latch of fig. 7.4, there is no way of entering the desired digital information, to be stored in it. If we replace the inverters G, and G, with 2-input NAND, gates, the other input terminals of the NAND gates, can be used to enter the, desired digital information as shown in figure 7.7., , , , , , , , , , , , , , , , , , A 6 Q, pHs aq, FIGURE 7.7, , Each flip-flop in its making, make use of latch as shown in figure 7.7., , 7.5 S-R Flip Flop, , The simplest type of flip-flop is Set-Reset (S-R) flip flop. It has two inputs, namely,, , S(set) and (Reset) and two outputs Q and Q which are complements to each, other as shown in figure 7.8., , , , , , , , , , , , , , , , , , , , , , , , s Q, SR, FLIP-FLOP _, R Q, FIGURE 7.8, , The circuit of S-R Flip Flop is made with the help of latch and two more NAND gates, as shown in figure 7.9., , , , , , , , , , , , Lactating!, , , , , , , , , , , , , , , , Scanned with CamScanner